PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 99

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

Internal Device Control Register (DCR) Interface

The PowerPC 405 Processor block contains several internal device-control registers, which

can be used to control, configure, and hold status for various functional units in the

Processor block. These registers are accessed on internal DCR busses, which share their

address range with the device-control registers accessed on the external DCR bus. This

means that the address locations assigned for internal PowerPC DCR registers must not be

populated by registers accessed over the external DCR bus.

Virtex-II Pro and Virtex-II ProX

In Virtex-II Pro and Virtex-II ProX processor blocks, there are two functional units that

contain device-control registers:

1. The data-side OCM (DSOCM) controller, which contains the DSCNTL and DSARC

registers.

2. The instruction-side OCM (ISOCM) controller, which contains the ISCNTL, ISARC,

ISINIT, and ISFILL registers.

See Chapter 3 for address mapping for these registers and for details on how Virtex-II Pro

and Virtex-II ProX address mapping differs from Virtex-4.

The registers contained by the DSOCM and ISOCM controllers are located in two address

blocks, which are independently located in the 10-bit DCR address space The locations are

defined by the input ports TIEDSOCMDCRADDR[0:7] and TIEISOCMDCRADDR[0:7].

They define the eight most significant address bits for the DSOCM and ISOCM register

block addresses respectively. The individual register offset in each block is defined by the

tables below:

For more information, please refer to the “OCM Controller Operation” section of

Chapter 3, “PowerPC 405 OCM Controller.”

Note: Virtex-II Pro and ProX address mapping differs from the mapping in Virtex-4-FX. To simplify

porting of a design from a Virtex-II Pro or ProX to a Virtex-4-FX part, the user must ensure that the

most significant six bits of the two TIE signals are identical and that TIEISOCMDCRADDR[6:7]=00

and TIEDSOCMDCRADDR[6:7]=01.

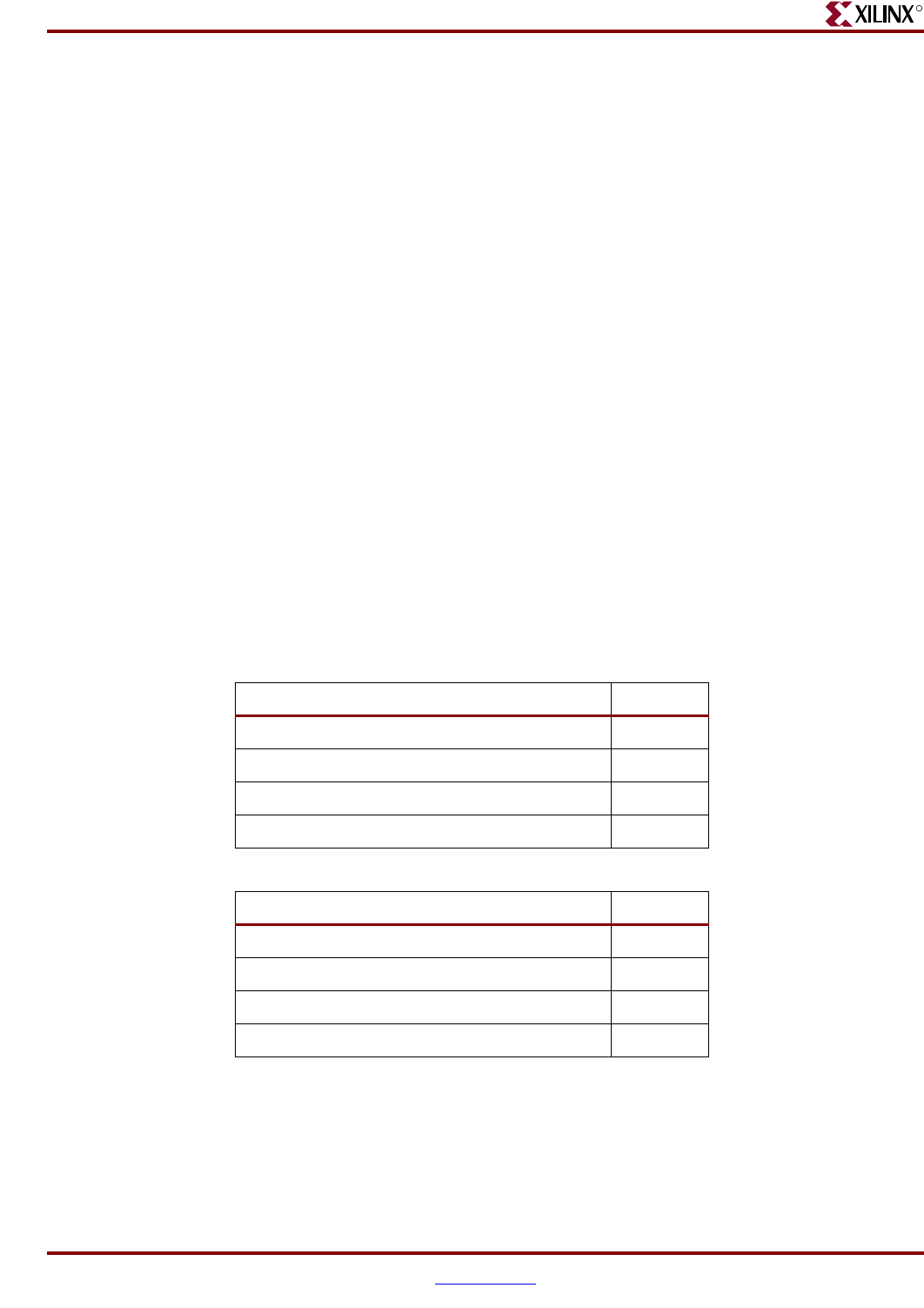

Table 2-18: Virtex-II Pro/ProX DSOCM DCR Address Offset

Device Control Register Offset

DSCNTL 3

DSARC 2

reserved 1

reserved 0

Table 2-19: Virtex-II Pro/ProX ISOCM DCR Address Offset

Device Control Register Offset

ISCNTL 3

ISARC 2

ISFILL 1

ISINIT 0