214 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

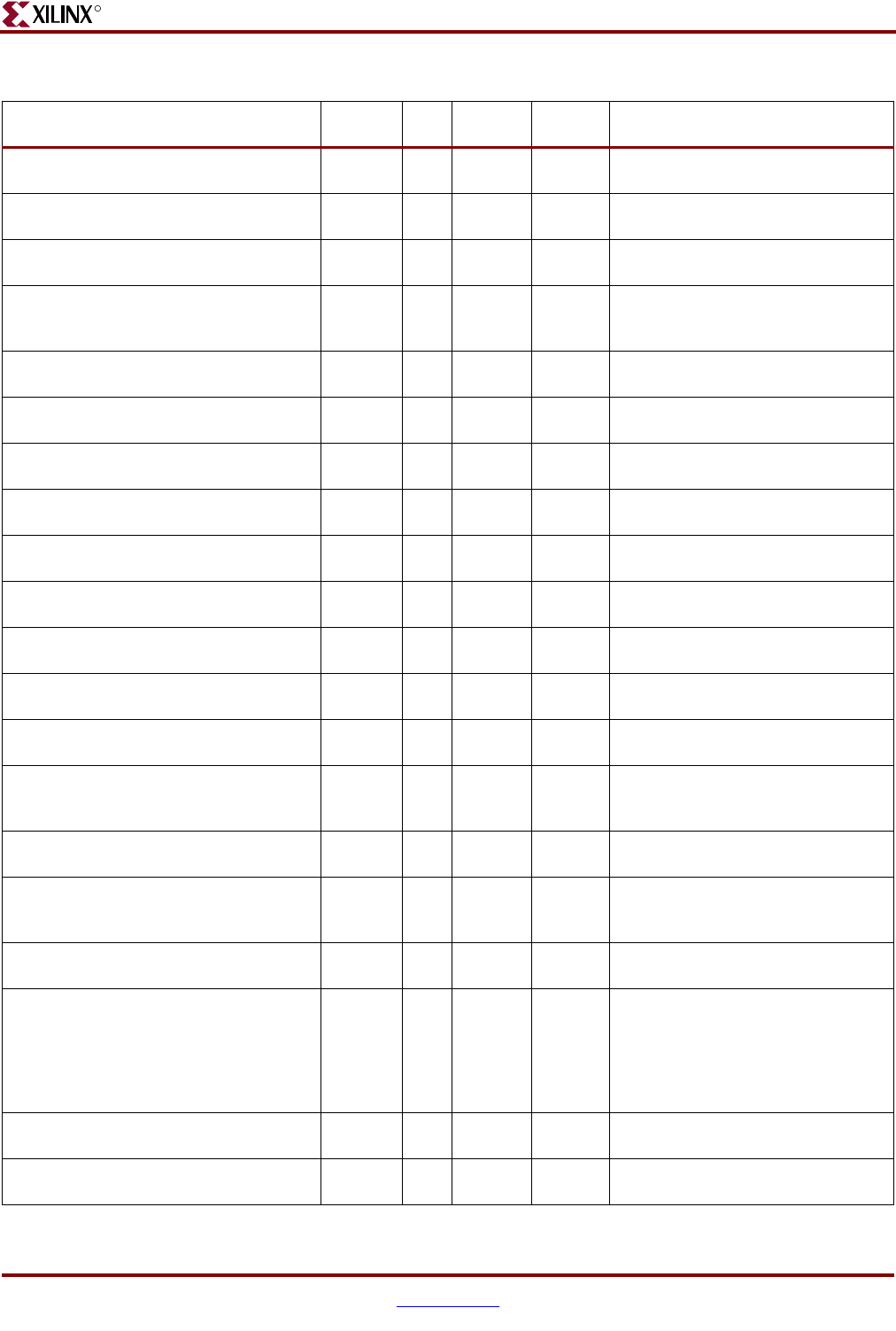

Appendix B: Signal Summary

R

APUFCMXERCA V-4 O FCM No

Connect

Reflects the XerCA bit used for

extended arithmetic.

BRAMDSOCMCLK V-II Pro

and V-4

I DSOCM 1 Clocks the DSOCM controller and the

data side interface logic

BRAMDSOCMRDDBUS[0:31] V-II Pro

and V-4

I DSOCM 0 Read data bus from the FPGA fabric to

the DSOCM controller.

BRAMISOCMCLK V-II Pro

and V-4

I ISOCM 1 Clocks the ISOCM controller and the

instruction side memory located in the

FPGA fabric.

BRAMISOCMDCRRDDBUS[0:31] V-4 I ISOCM 0 Read data from BRAM to ISOCM

controller using a DCR-based access.

BRAMISOCMRDDBUS[0:63] V-II Pro

and V-4

I ISOCM 0 Read data from BRAM to the ISOCM

controller

C405CPMCORESLEEPREQ V-II Pro

and V-4

OCPM No

Connect

Indicates the core is requesting to be

put into sleep mode.

C405CPMMSRCE V-II Pro

and V-4

OCPM No

Connect

Indicates the value of MSR[CE].

C405CPMMSREE V-II Pro

and V-4

OCPM No

Connect

Indicates the value of MSR[EE].

C405CPMTIMERIRQ V-II Pro

and V-4

OCPM No

Connect

Indicates a timer-interrupt request

occurred.

C405CPMTIMERRESETREQ V-II Pro

and V-4

OCPM No

Connect

Indicates a watchdog-timer reset

request occurred.

C405DBGMSRWE V-II Pro

and V-4

ODebugNo

Connect

Indicates the value of MSR[WE].

C405DBGSTOPACK V-II Pro

and V-4

ODebugNo

Connect

Indicates the PowerPC 405 is in debug

halt mode.

C405DBGWBCOMPLETE V-II Pro

and V-4

ODebugNo

Connect

Indicates the current instruction in the

PowerPC 405 writeback pipeline stage

is completing.

C405DBGWBFULL V-II Pro

and V-4

ODebugNo

Connect

Indicates the PowerPC 405 writeback

pipeline stage is full.

C405DBGWBIAR[0:29] V-II Pro

and V-4

ODebugNo

Connect

The address of the current instruction

in the PowerPC 405 writeback pipeline

stage.

C405DCRABUS[0:9]

EXTDCRABUS[0:9]

V-II Pro

and V-4

ODCR No

Connect

Specifies the address of the DCR access

request.

C405DCRDBUSOUT[0:31]

EXTDCRDBUSOUT[0:31]

V-II Pro

and V-4

ODCR No

Connect

or attach

to

input

bus

The 32-bit DCR write-data bus.

C405DCRREAD

EXTDCRREAD

V-II Pro

and V-4

ODCR No

Connect

Indicates a DCR read request occurred.

C405DCRWRITE

EXTDCRWRITE

V-II Pro

and V-4

ODCR No

Connect

Indicates a DCR write request

occurred.

Table B-1: PowerPC 405 Interface Signals in Alphabetical Order (Continued)

Signal

FPGA

Type

a

I/O

Type

Interface

If Unused

Ties To:

b

Function