228 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Appendix C: Processor Block Timing Model

R

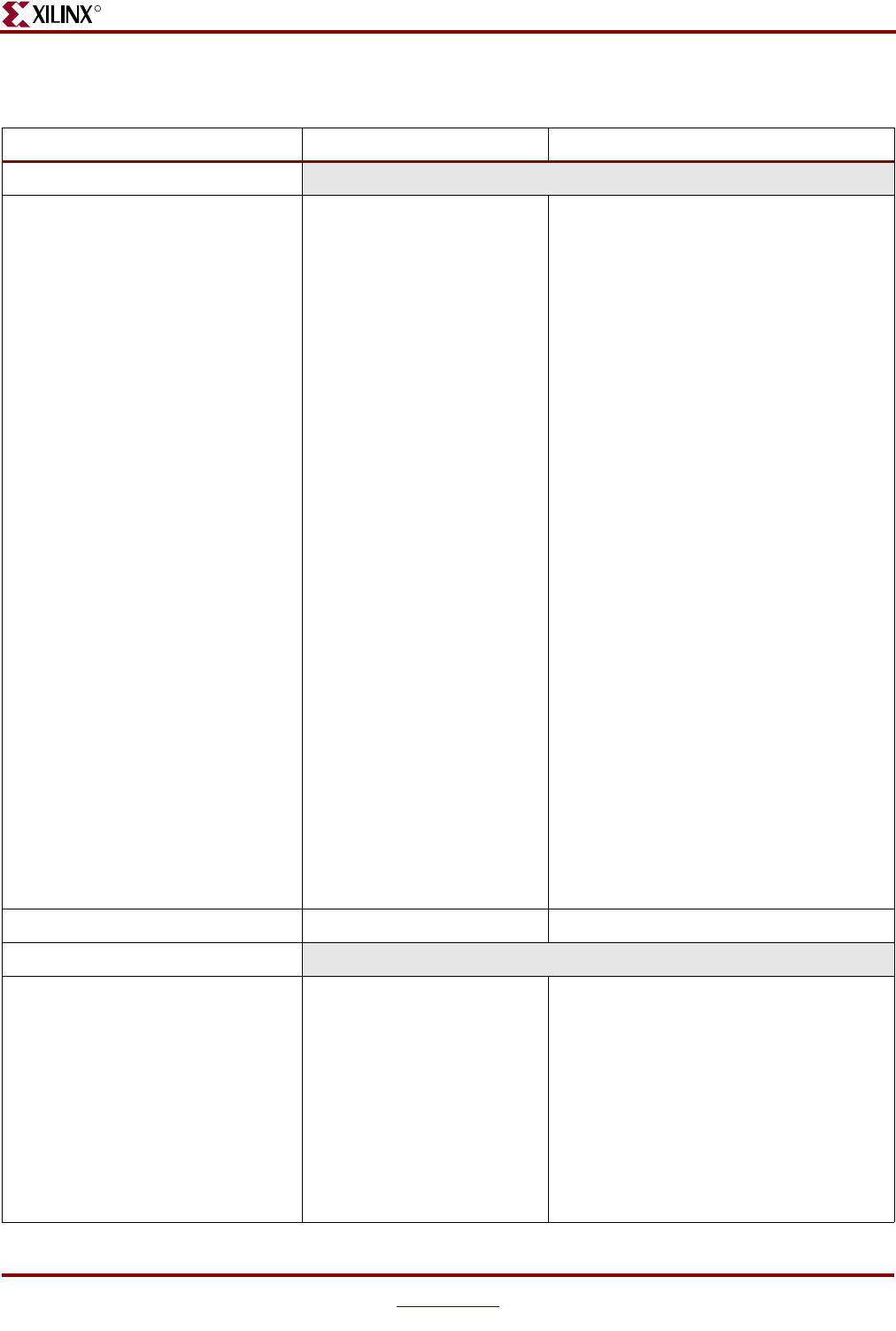

Table C-4: Parameters Relative to the FCM Clock (CPMFCMCLK, Virtex-4 Only)

Parameter Function Signals

Setup/Hold:

T

PCCK_

FCM/T

PCKC

_FCM Control Inputs FCMAPUINSTRACK

FCMAPUDONE

FCMAPUSLEEPNOTREADY

FCMAPUDECODEBUSY

FCMAPUDCDGPRWRITE

FCMAPUDCDRAEN

FCMAPUDCDRBEN

FCMAPUDCDPRIVOP

FCMAPUDCDFORCEALIGN

FCMAPUDCDXEROVEN

FCMAPUDCDXERCAEN

FCMAPUDCDCREN

FCMAPUEXECRFIELD[0:2]

FCMAPUDCDLOAD

FCMAPUDCDSTORE

FCMAPUDCDUPDATE

FCMAPUDCDLDSTBYTE

FCMAPUDCDLDSTHW

FCMAPUDCDLDSTWD

FCMAPUDCDLDSTDW

FCMAPUDCDLDSTQW

FCMAPUDCDTRAPLE

FCMAPUDCDTRAPBE

FCMAPUDCDFORCEBESTEERING

FCMAPUFPUOP

FCMAPUEXEBLOCKINGMCO

FCMAPULOADWAIT

FCMAPURESULTVALID

FCMAPUXEROV

FCMAPUEXENONBLOCKINGMCO

FCMAPUXERCA

FCMAPUCR[0:3]

FCMAPUEXCEPTION

T

PDCK_

FCM/T

PCKO

_FCM Data Inputs FCMAPURESULT[0:31]

Clock to Out:

T

PCKCO

_FCM Control Outputs APUFCMINSTRVALID

APUFCMOPERANDVALID

APUFCMFLUSH

APUFCMWRITEBACKOK

APUFCMLOADDVALID

APUFCMLOADBYTEEN[0:3]

APUFCMENDIAN

APUFCMXERCA

APUFCMDECODED

APUFCMDECUDI[0:2]

APUFCMDECUDIVALID