230 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Appendix C: Processor Block Timing Model

R

T

PCKDO

_PLB Data outputs C405PLBDCUWRDBUS[0:63]

T

PCKAO

_PLB Address outputs C405PLBDCUABUS[0:31]

C405PLBICUABUS[0:29]

Clock:

T

PPWH

Clock pulse width, High state PLBCLK

T

PPWL

Clock pulse width, Low state PLBCLK

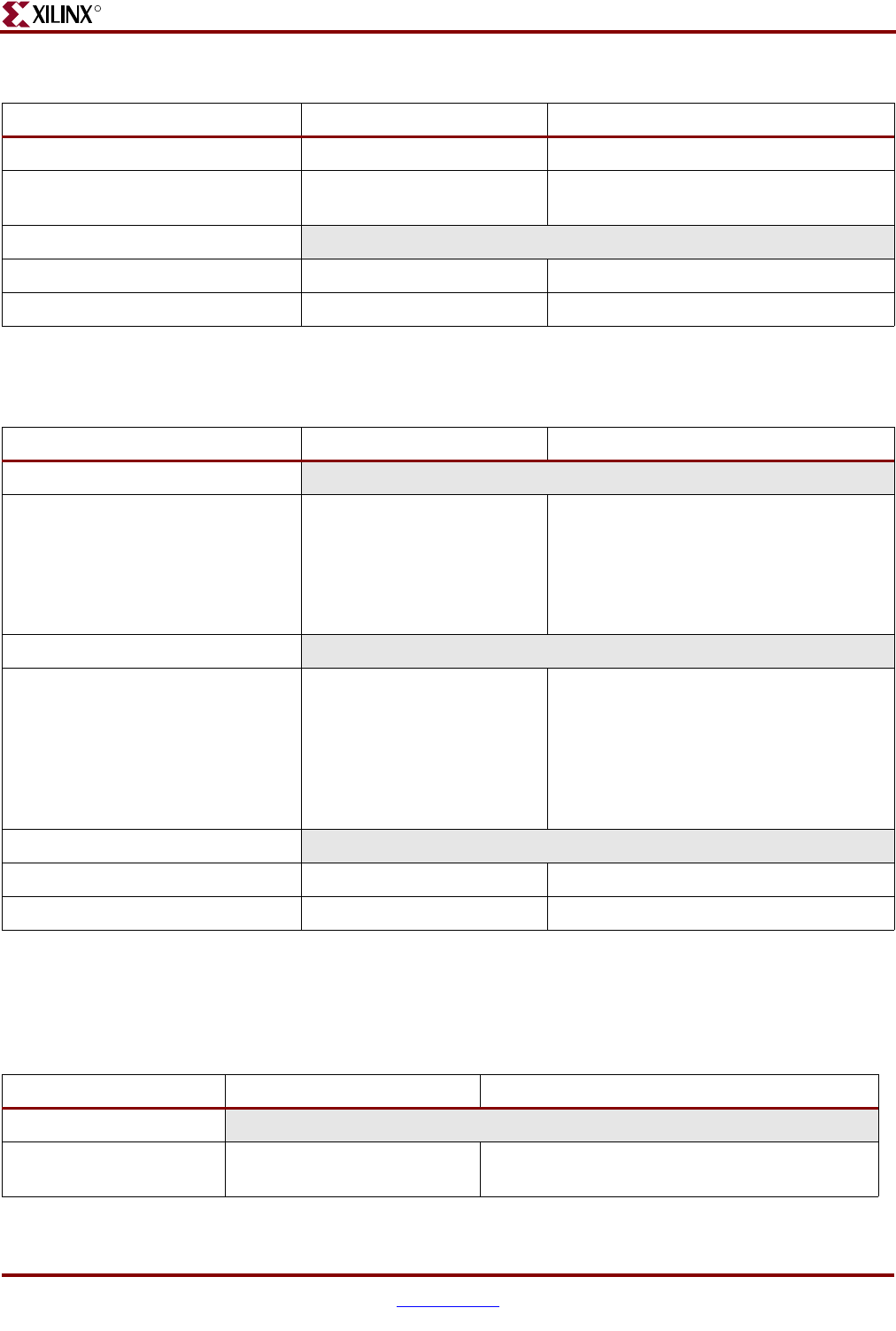

Table C-5: Parameters Relative to the PLB Clock (PLBCLK) (Continued)

Parameter Function Signals

Table C-6: Parameters Relative to the JTAG Clock (JTAGC405TCK)

Parameter Function Signals

Setup/Hold:

T

PCCK

_JTAG/T

PCKC

_JTAG Control inputs JTGC405BNDSCANTDO

JTGC405TDI

JTGC405TMS

JTGC405TRSTNEG

CPMC405CORECLKINACTIVE

DBGC405EXTBUSHOLDACK

Clock to Out:

T

PCKCO

_JTAG Control outputs C405JTGCAPTUREDR

C405JTGEXTEST

(1)

C405JTGPGMOUT

(2)

C405JTGSHIFTDR

C405JTGTDO

(1)

C405JTGTDOEN

(1)

C405JTGUPDATEDR

Clock:

T

JPWH

Clock pulse width, High state JTGC405TCK

T

JPWL

Clock pulse width, Low state JTGC405TCK

Notes:

1. Synchronous to the negative edge of JTGC405TCK

2. Synchronous to CPMC405CLOCK

Table C-7: Parameters Relative to the ISOCM Clock (BRAMISOCMCLK)

Parameter Function Signals

Setup/Hold:

T

PDCK

_ISOCM

T

PCKD

_ISOCM

Data inputs BRAMISOCMRDDBUS[0:63]