156 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 3: PowerPC 405 OCM Controller

R

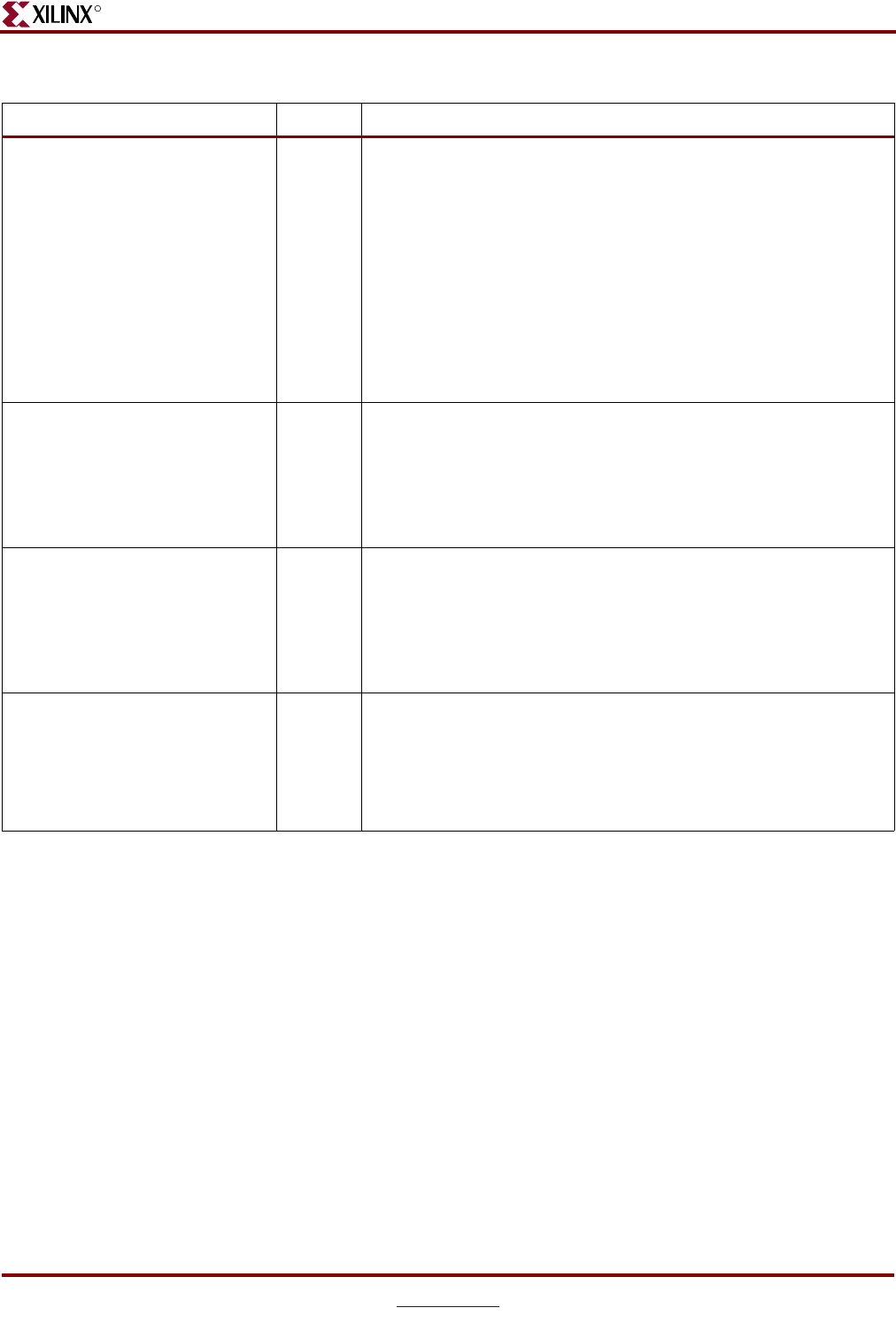

ISOCMBRAMEVENWRITEEN Output

Note: Optional. Used in dual-port BRAM interface designs only.

Write enable to qualify a valid write into a block RAM via a DCR-

based access. This signal enables a write into the 32-bit memory that

contains even instruction words BRAMISOCMRDDBUS[0:31].

For Virtex-II Pro, connect this signal to both the Enable (EN) and

Write (WE) inputs of a dual-port ISBRAM port for power savings.

For Virtex-4, connect this signal to Write (WE) inputs of a dual-port

ISBRAM port and ISOCMDCRBRAMEVENEN to the Enable (EN)

input of the dual-port ISBRAM port.

For single-port ISBRAM implementations, this signal can be left

unconnected.

ISOCMDCRBRAMODDEN

(Virtex-4 only)

Output

Note: Optional. Used in dual-port BRAM interface designs only.

BRAM enable (odd bank) to qualify a valid read or write from a

BRAM via a DCR-based access, in order to access odd instruction

words.

For Virtex-4, connect this signal to the Enable (EN) input of the dual-

port ISBRAM port.

ISOCMDCRBRAMEVENEN

(Virtex-4 only)

Output

Note: Optional. Used in dual-port BRAM interface designs only.

BRAM enable (even bank) to qualify a valid read or write from

BRAM via a DCR-based access, in order to access even instruction

words.

For Virtex-4, connect this signal to the Enable (EN) input of the dual-

port ISBRAM port.

ISOCMDCRBRAMRDSELECT

(Virtex-4 only)

Output

Note: Optional. Used in dual-port BRAM interface designs only.

Since the DCR bus can only access 32-bit data and the ISOCM has a

64-bit data bus, this output signal, driven by the ISOCM controller,

must be used to select between even and odd instruction words

using a multiplexer in the FPGA fabric. At logic 1, it selects the odd

instruction word; at logic 0, it selects the even instruction word.

Table 3-8: ISOCM Output Ports (Continued)

Port Direction Description