58 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 2: Input/Output Interfaces

R

transfer order is invalid if this signal asserted. The entries for a 32-bit PLB slave assume the

connection to a 64-bit master shown in Figure 2-5, above.

PLBC405ICUBUSY (Input)

When asserted, this signal indicates the PLB slave acknowledged and is responding to (is

busy with) an ICU fetch request. When deasserted, the PLB slave is not responding to an

ICU fetch request.

This signal should be asserted in the cycle after an ICU fetch request is acknowledged by

the PLB slave and remain asserted until the request is completed by the PLB slave. It

should be deasserted in the cycle after the last read-data acknowledgement signal is

asserted by the PLB slave, completing the transfer. If multiple fetch requests are initiated

and overlap, the busy signal should be asserted in the cycle after the first request is

acknowledged and remain asserted until the cycle after the final read-data

acknowledgement is completed for the last request.

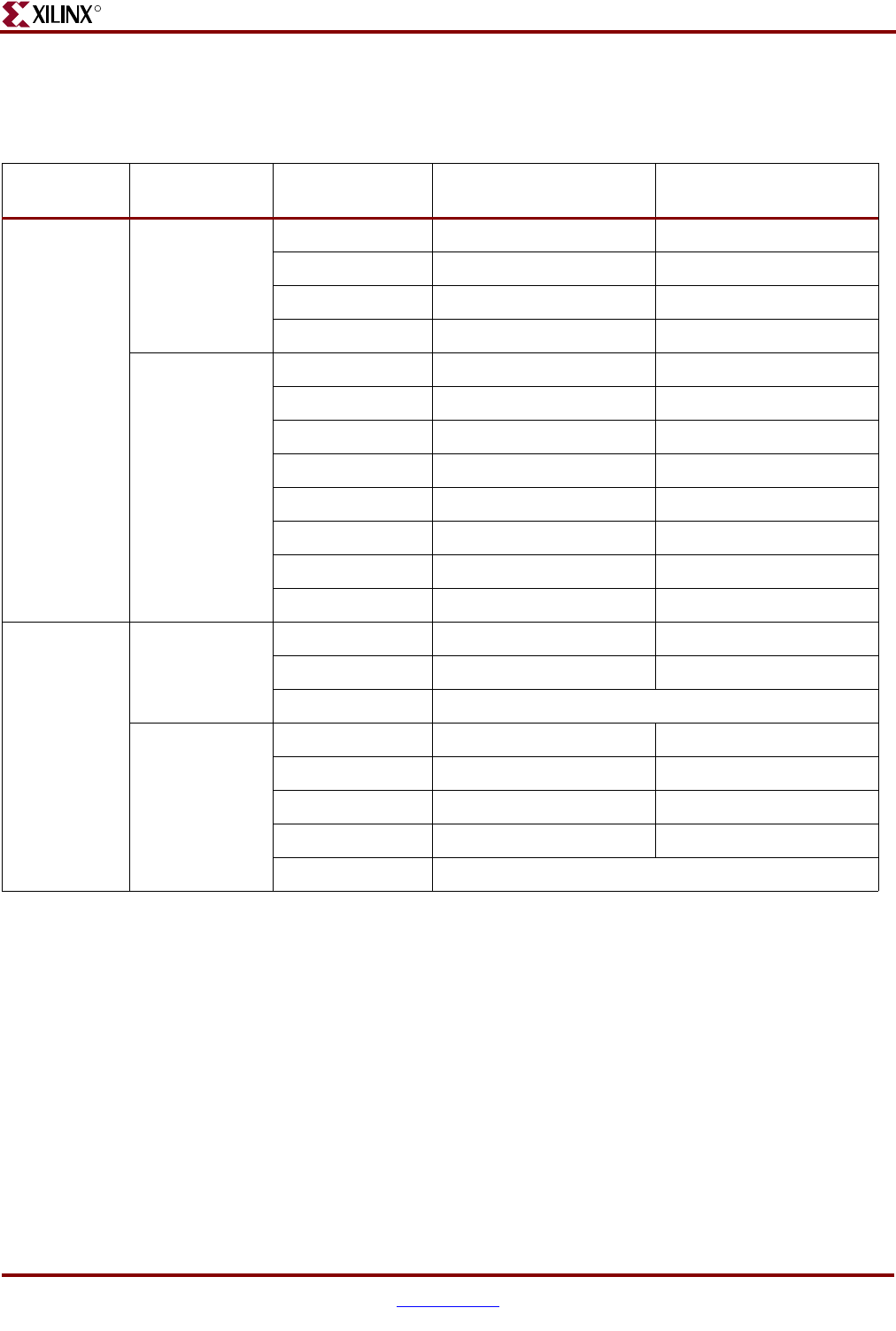

Table 2-10: Contents of ICU Read-Data Bus During Line Transfer

PLB Slave

Size

Line Transfer

Size

Transfer Order

a

ICU Read-Data Bus [0:31]

ICU Read-Data Bus

[32:63]

32-Bit Four Words x00 Instruction 0 Instruction 0

x01 Instruction 1 Instruction 1

x10 Instruction 2 Instruction 2

x11 Instruction 3 Instruction 3

Eight Words 000 Instruction 0 Instruction 0

001 Instruction 1 Instruction 1

010 Instruction 2 Instruction 2

011 Instruction 3 Instruction 3

100 Instruction 4 Instruction 4

101 Instruction 5 Instruction 5

110 Instruction 6 Instruction 6

111 Instruction 7 Instruction 7

64-Bit Four Words x00 Instruction 0 Instruction 1

x10 Instruction 2 Instruction 3

xx1 Invalid

Eight Words 000 Instruction 0 Instruction 1

010 Instruction 2 Instruction 3

100 Instruction 4 Instruction 5

110 Instruction 6 Instruction 7

xx1 Invalid

a. An “x” indicates a don’t-care value in PLBC405ICURDWDADDR[1:3].