152 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 3: PowerPC 405 OCM Controller

R

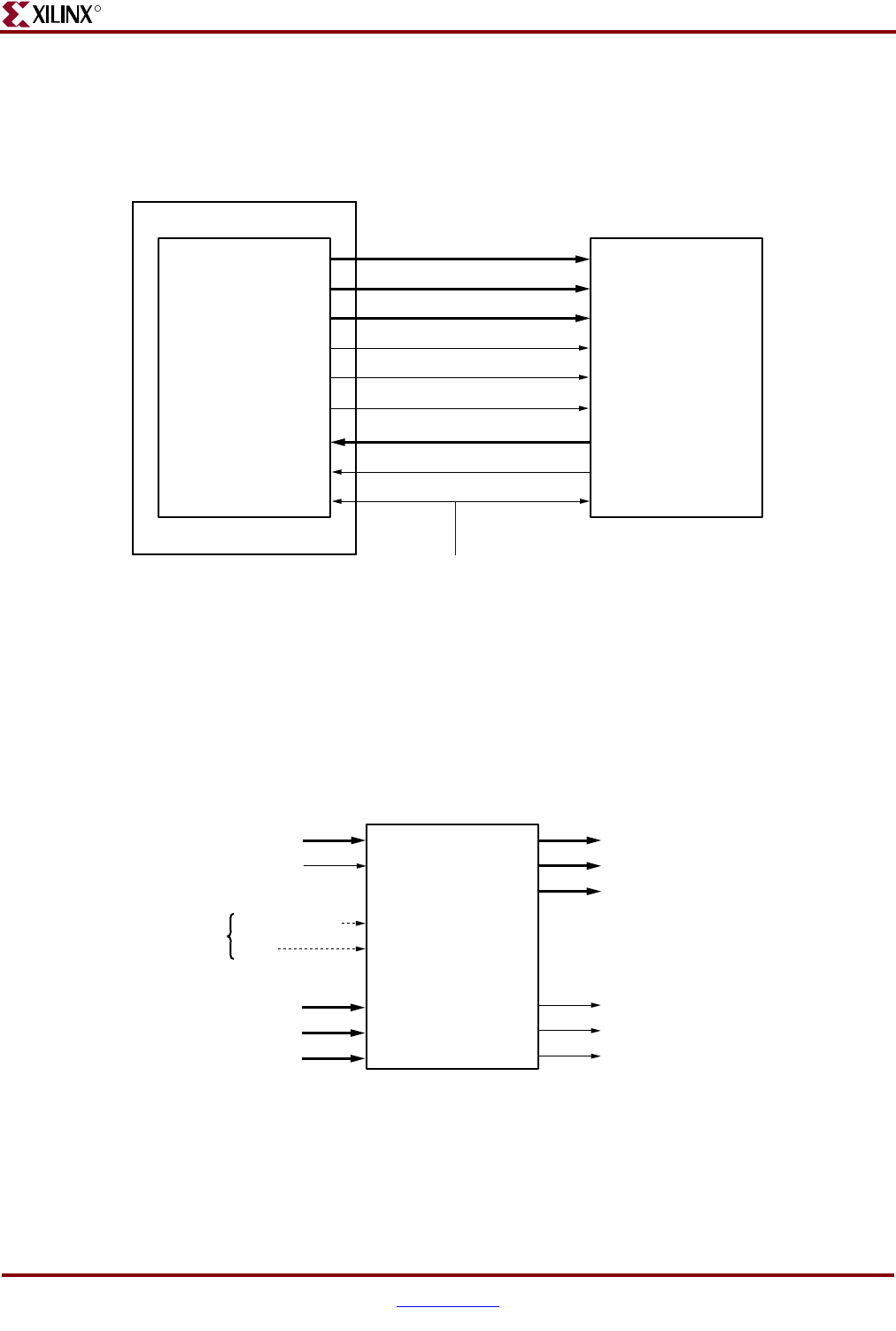

Figure 3-6 shows the extended feature in Virtex-4 for DSOCM-to-Memory-Mapped-Slave-

Peripheral interface.

ISOCM Ports

Figure 3-7 and Figure 3-8 are block diagrams of the ISOCM in Virtex-II Pro and Virtex-4.

All signals are in big endian format.

Figure 3-6: DSOCM to Memory-Mapped Slave Peripheral (Virtex-4 Extended Feature)

DSOCMBRAMEN

UG018_37c_042304

DSOCMBRAMABUS[8:29]

Virtex-4 Processor Block

DSOCMBRAMWRDBUS[0:31]

DSOCMBRAMBYTEWRITE[0:3]

BRAMDSOCMRDDBUS[0:31]

DSOCMRDADDRVALID

DSOCMWRADDRVALID

DSOCMRDWRCOMPLETE

BRAMDSOCMCLK

Data-Side

On-Chip Memory

(DSOCM) Controller

Memory Mapped

OCM Slave

(Variable Latency)

Figure 3-7: ISOCM Interface for Virtex-II Pro

ISOCMBRAMEN

ISOCMBRAMODDWRITEEN

UG018_38_020102

RESET

ISOCMBRAMRDABUS[8:28]

BRAMISOCMRDDBUS[0:63]

ISOCMBRAMWRABUS[8:28]

ISOCMBRAMWRDBUS[0:31]

BRAMISOCMCLK

CPMC405CLOCK

ISCNTLVALUE[0:7]

ISARCVALUE[0:7]

TIEISOCMDCRADDR[0:7]

ISOCMBRAMEVENWRITEEN

Clock & Reset are

same signals that go

into CPU; therefore,

no separate Clock &

Reset are required.

Instruction-Side

On-Chip Memory

(ISOCM) Controller