194 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 4: PowerPC 405 APU Controller

R

APU Controller Input Signals

All APU Controller input signals should be synchronized on the FCM clock

(CPMFCMCLK).

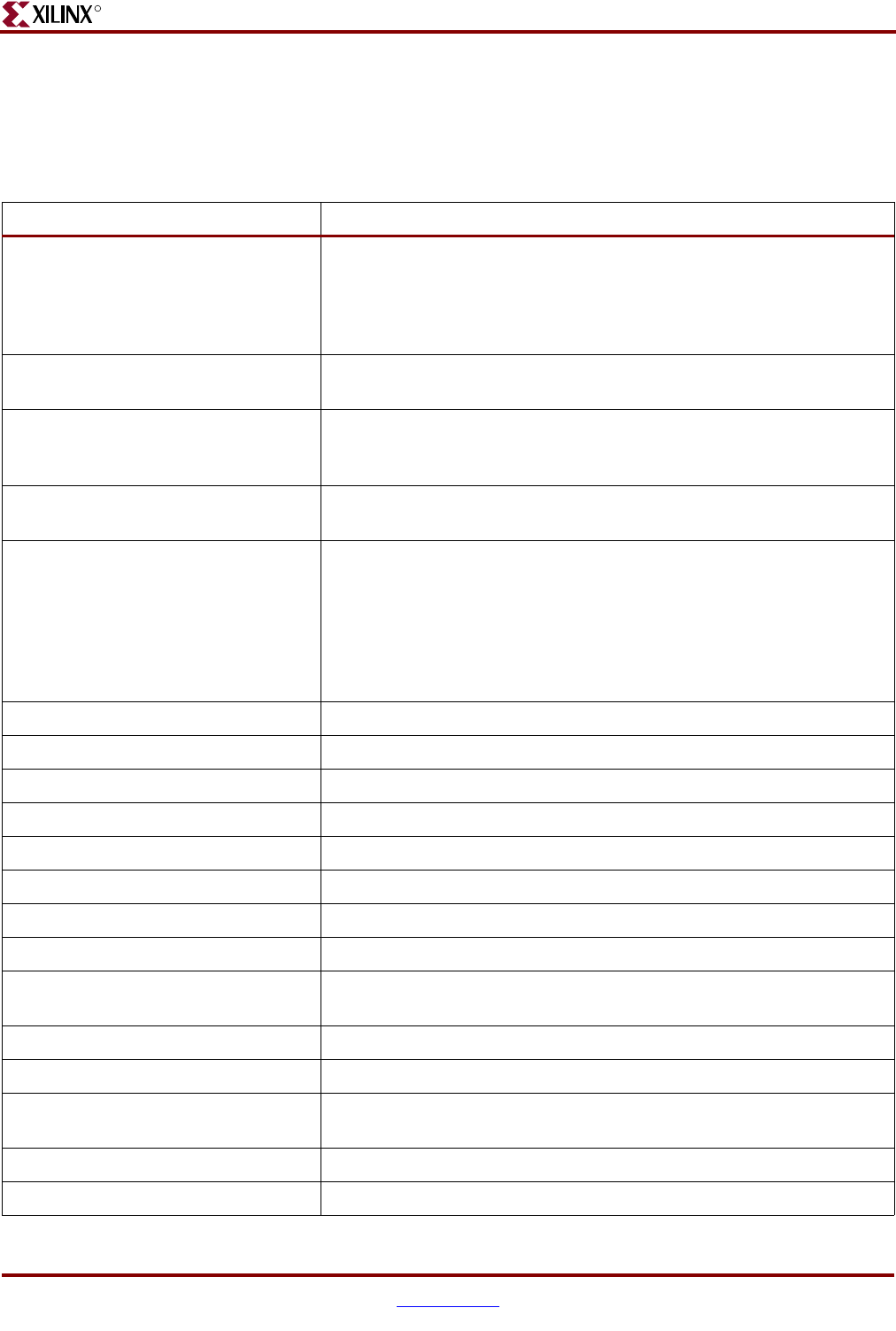

Table 4-6: FCM Interface Input Signals

Signal Function

FCMAPUINSTRACK Valid instruction decoded in FCM. Must be asserted the first cycle in

which FCMAPUDECODEBUSY is low, after APUFCMINSTRVALID

has been asserted. All instruction decode signals from the FCM to APU

Controller must be valid when asserted. If the instruction is decoded by

the APU Controller, there is no need to send this signal; it is ignored.

FCMAPURESULT[0:31] FCM execution result being passed to the CPU through the APU

Controller.

FCMAPUDONE Indicates the completion of the instruction in the FCM to the APU

Controller. In the case of an autonomous instruction, FCMAPUDONE

simply means that the FCM can receive another instruction.

FCMAPUSLEEPNOTREADY Indicates to the APU Controller that the FCM is still executing. It is used

to determine when the CPU is allowed to enter sleep mode.

FCMAPUDECODEBUSY Allows FCM to do a multi-cycle instruction decode before returning

FCMAPUINSTRACK. Two modes: with or without instruction hold. If

this signal is low when APUFCMINSTRVALID asserts, the

APUFCMINSTRUCTION data is only valid for that cycle; if, on the

other hand, FCMAPUBUSYDECODE is high then

APUFCMINSTRUCTION is held until FCMAPUDECODEBUSY is

lowered.

FCMAPUDCDGPRWRITE FCM decoded instruction must write back to the GPR.

FCMAPUDCDRAEN FCM decoded instruction need data from GPR(Ra).

FCMAPUDCDRBEN FCM decoded instruction need data from GPR(Rb).

FCMAPUDCDPRIVOP FCM decoded instruction executes in privileged mode.

FCMAPUDCDFORCEALIGN FCM decoded load/store instruction with forced word alignment.

FCMAPUDCDXEROVEN FCM decoded instruction returns overflow status.

FCMAPUDCDXERCAEN FCM decoded instruction returns carry status.

FCMAPUDCDCREN FCM decoded instruction sets condition register (CR) bits.

FCMAPUEXECRFIELD[0:2] FCM decoded instruction selects which of the eight PowerPC CR field

to update: 0=CR0, 1=CR1, etc.

FCMAPUDCDLOAD FCM decoded load instruction.

FCMAPUDCDSTORE FCM decoded store instruction.

FCMAPUDCDUPDATE FCM decoded load/store instruction should update Ra with effective

address.

FCMAPUDCDLDSTBYTE FCM decoded load/store instruction does byte transfer.

FCMAPUDCDLDSTHW FCM decoded load/store instruction does half word transfer.