42 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 2: Input/Output Interfaces

R

CPU Control Interface I/O Signal Descriptions

The following sections describe the operation of the CPU control-interface I/O signals.

TIEC405MMUEN (Input)

When held active (tied to logic 1), this signal enables the PowerPC 405 memory-

management unit (MMU). When held inactive (tied to logic 0), this signal disables the

MMU. The MMU is used for virtual to address translation and for memory protection. Its

operation is described in the PowerPC Processor Reference Guide.

TIEC405DETERMINISTICMULT (Input)

Note: This signal should always be driven low. Setting it high may produce erroneous results.

When held active (tied to logic 1), this signal disables the hardware multiplier early-out

capability. All multiply instructions have a 4-cycle reissue rate and a 5-cycle latency rate.

When held inactive (tied to logic 0), this signal enables the hardware multiplier early-out

capability. If early out is enabled, multiply instructions are executed in the number of

cycles specified in Table 2-4. The performance of multiply instructions is described in the

PowerPC Processor Reference Guide.

Note: In Table 2-4, above, words are treated as halfwords if the upper 16 bits of the operand contain

a sign extension of the lower 16 bits. For example, if the upper 16 bits of a word operand are zero, the

operand is considered a halfword when calculating the execution time.

TIEC405DISOPERANDFWD (Input)

When held active (tied to logic 1), this signal disables operand forwarding. When held

inactive (tied to logic 0), this signal enables operand forwarding. The processor uses

operand forwarding to send load-instruction data from the data cache to the execution

units as soon as it is available. Operand forwarding often saves a clock cycle when

TIEC405DISOPERANDFWD I Required Disables operand forwarding for load instructions.

C405XXXMACHINECHECK O No Connect Indicates a machine-check error has been detected by

the PowerPC 405.

Table 2-3: CPU Control Interface I/O Signals (Continued)

Signal

I/O

Type

If Unused Function

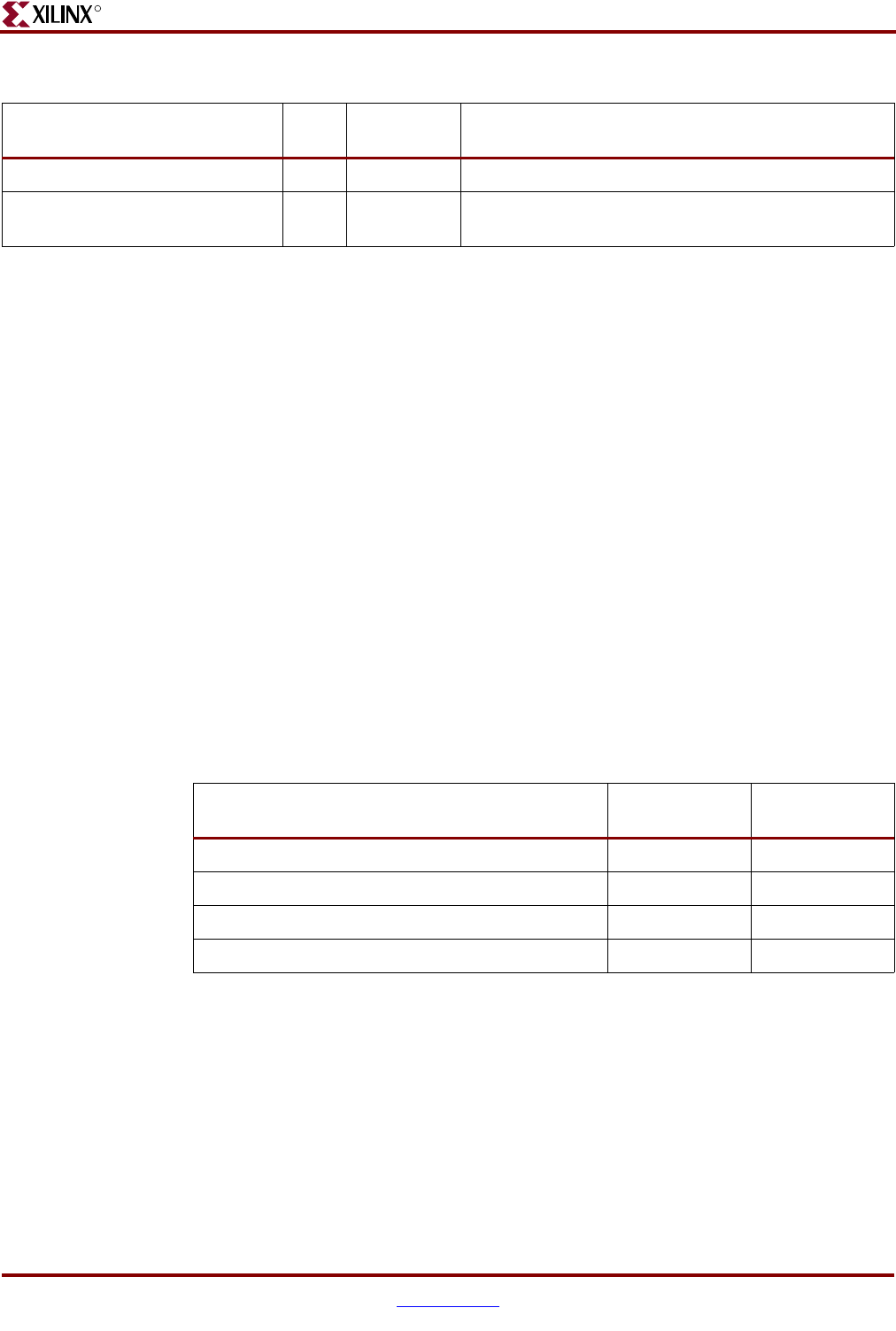

Table 2-4: Multiply and MAC Instruction Timing

Operations

Issue-Rate

Cycles

Latency

Cycles

MAC and Negative MAC 1 2

Halfword

uHalfword (32-bit result) 1 2

Halfword

uWord (48-bit result) 2 3

Word

uWord (64-bit result) 4 5