196 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 4: PowerPC 405 APU Controller

R

APU Controller Output Signals

All APU Controller output signals are synchronous with the FCM clock (CPMFCMCLK).

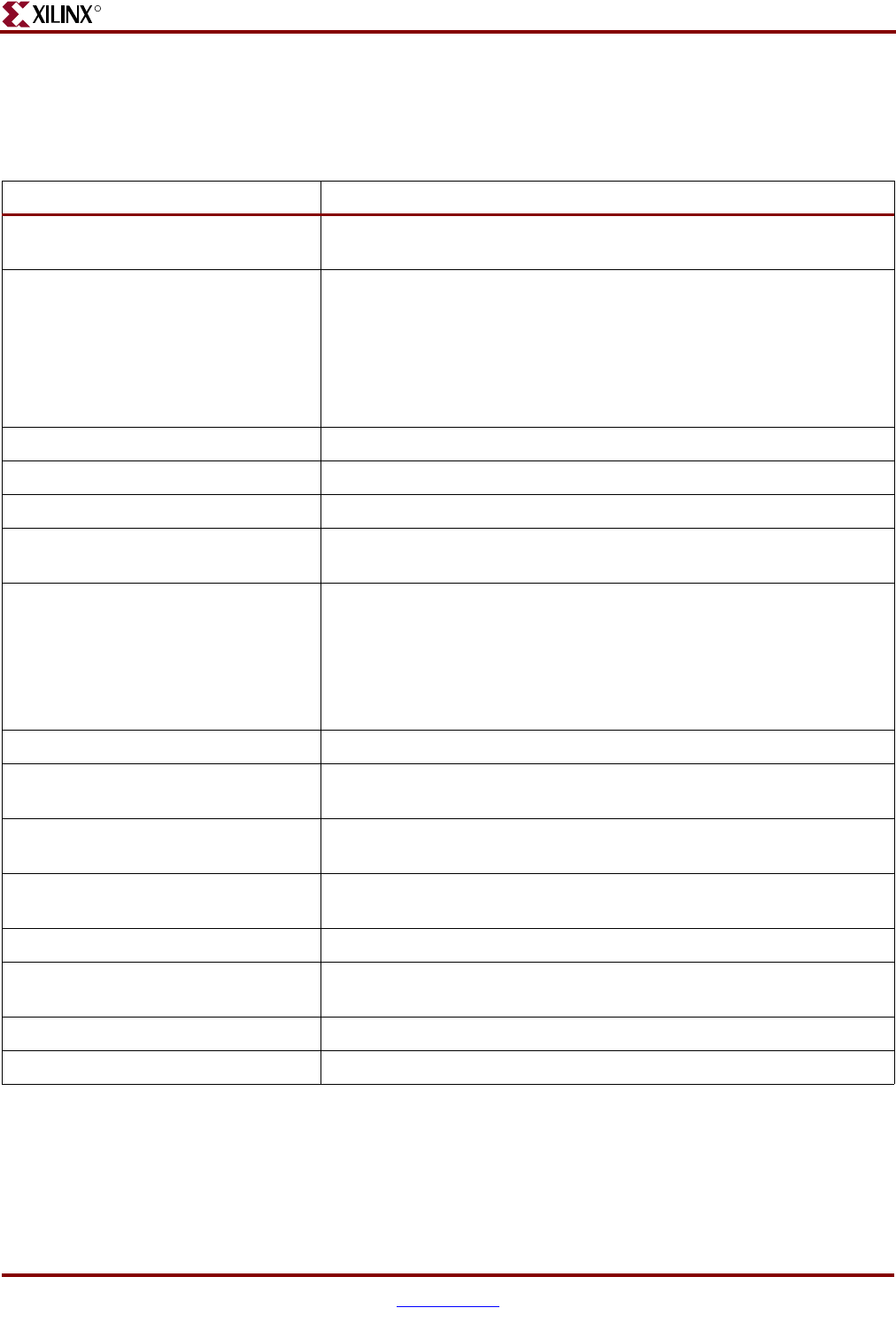

Table 4-7: FCM Interface Output Signals

Signal Function

APUFCMINSTRUCTION[0:31] Instruction being presented to the FCM. Is valid as long as

APUFCMINSTRVALID is high.

APUFCMINSTRVALID This signal is asserted on two conditions:

x A valid APU instruction was decoded by the APU Controller

x An undecoded instruction passed to FCM for decoding

The signal will remain high for one FCM clock cycle, unless

FCMAPUDECODEBUSY is high when it asserts. In that case it stays

high until FCMAPUDECODEBUSY goes low.

APUFCMRADATA[0:31] Instruction operand from GPR(RA).

APUFCMRBDATA[0:31] Instruction operand from GPR(RB).

APUFCMOPERANDVALID Instruction operand valid.

APUFCMFLUSH Flush APU instruction in the FCM. If asserted no

APUFCMWRITEBACKOK signal will be generated

APUFCMWRITEBACKOK Safe for FCM to commit internal state change; the APU Controller can

no longer flush the instruction.

In normal cases, this signal is asserted for one FCM clock cycle. In some

cases when a non-blocking multi-cycle operation is followed by an

autonomous or blocking multi-cycle operation while using a large clock

ratio, the signal may be asserted for two back-to-back FCM clock cycles.

APUFCMLOADDATA[0:31] Data word loaded from storage to the APU register file.

APUFCMLOADDVALID When asserted the data word on the APUFCMLOADDATA[0:31] data

bus is valid.

APUFCMLOADBYTEEN[0:3] Specifies the valid bytes for the word on the load data bus

APUFCMLOADDATA[0:31].

APUFCMENDIAN When asserted, the load/store instruction being presented to the FCM

has true little-endian storage attribute.

APUFCMXERCA Reflects the XerCA bit used for extended arithmetic.

APUFCMDECODED Asserted when the APU Controller decoded the instruction being sent

to the FCM.

APUFCMDECUDI[0:2] Specifies which UDI the APU Controller decoded (binary encoded).

APUFCMDECUDIVALID Valid signals for APUFCMDECUDI.