PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 195

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

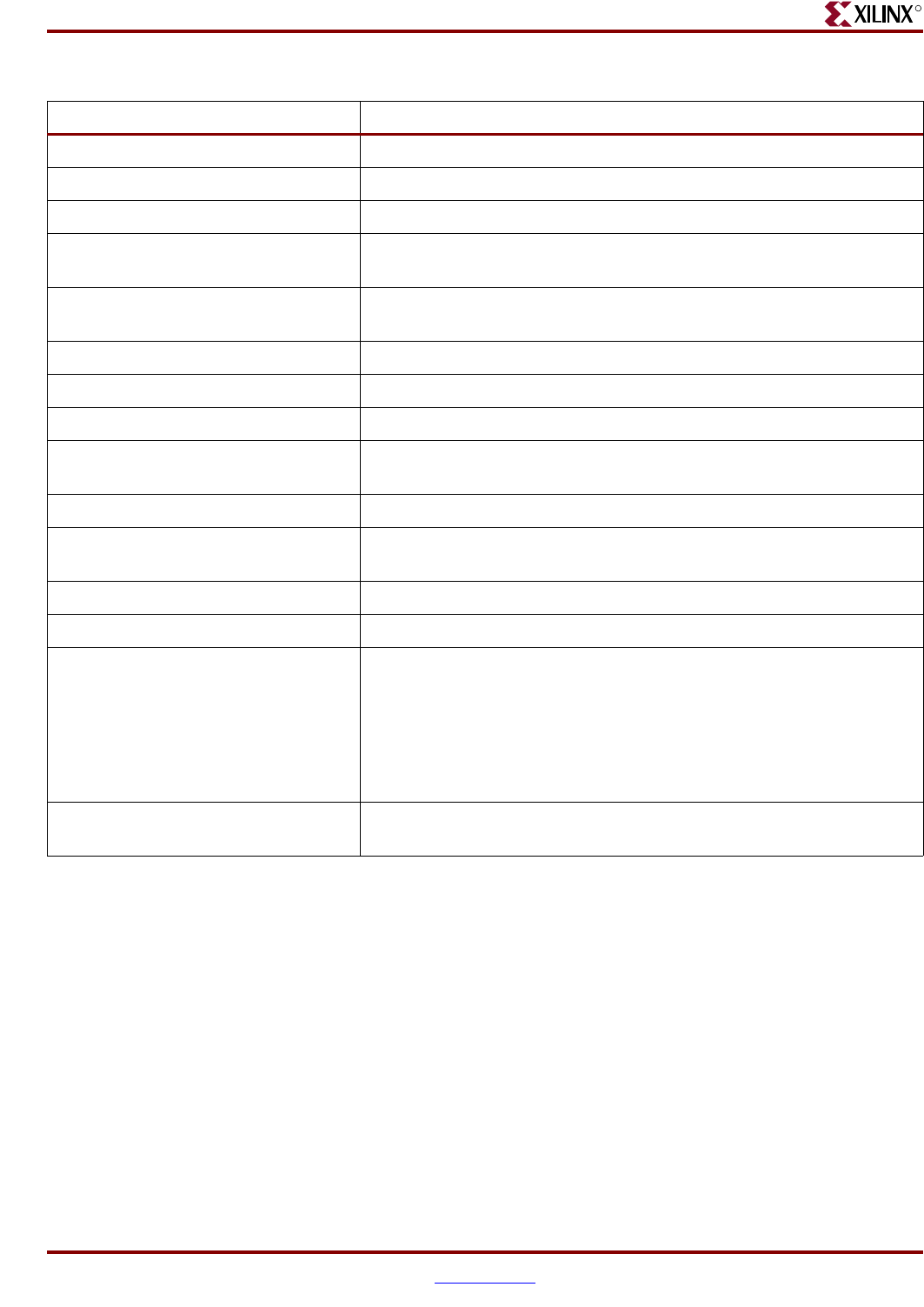

FCMAPUDCDLDSTWD FCM decoded load/store instruction does word transfer.

FCMAPUDCDLDSTDW FCM decoded load/store instruction does double word transfer.

FCMAPUDCDLDSTQW FCM decoded load/store instruction does quad word transfer.

FCMAPUDCDTRAPLE FCM decoded load/store instruction will cause alignment exception if

the storage Endian attribute is 1’b1.

FCMAPUDCDTRAPBE FCM decoded load/store instruction will cause alignment exception if

the storage Endian attribute is 1’b0.

FCMAPUDCDFORCEBESTEERING FCM decoded store instruction will force Big-Endian steering.

FCMAPUFPUOP FCM decoded FPU instruction.

FCMAPUEXEBLOCKINGMCO FCM decoded instruction for multi cycle operation of blocking class.

FCMAPUEXENONBLOCKINGMCO FCM decoded instruction for multi cycle operation of non-blocking

class.

FCMAPULOADWAIT FCM is not yet ready to receive next load data.

FCMAPURESULTVALID Values on the FCMAPURESULT[0:31], FCMAPUXEROV,

FCMAPUXERCA and FCMAPUCR[0:3] are valid.

FCMAPUXEROV FCM execution overflow status bit.

FCMAPUXERCA FCM execution carry status bit.

FCMAPUCR[0:3] Condition result bits to set in the PowerPC CR field selected by

FCMAPUEXECRFIELD:

x Bit 0 = set LT-bit, meaning result is less than zero

x Bit 1 = set GT-bit, meaning result is greater than 0

x Bit 2 = set EQ-bit, meaning result is zero

x Bit 3 = set SO-bit, meaning Summary Overflow

FCMAPUEXCEPTION FCM generate program exception on the processor (vector 0x0700).

Exception must be enabled by processor to trap.

Table 4-6: FCM Interface Input Signals (Continued)

Signal Function