162 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 3: PowerPC 405 OCM Controller

R

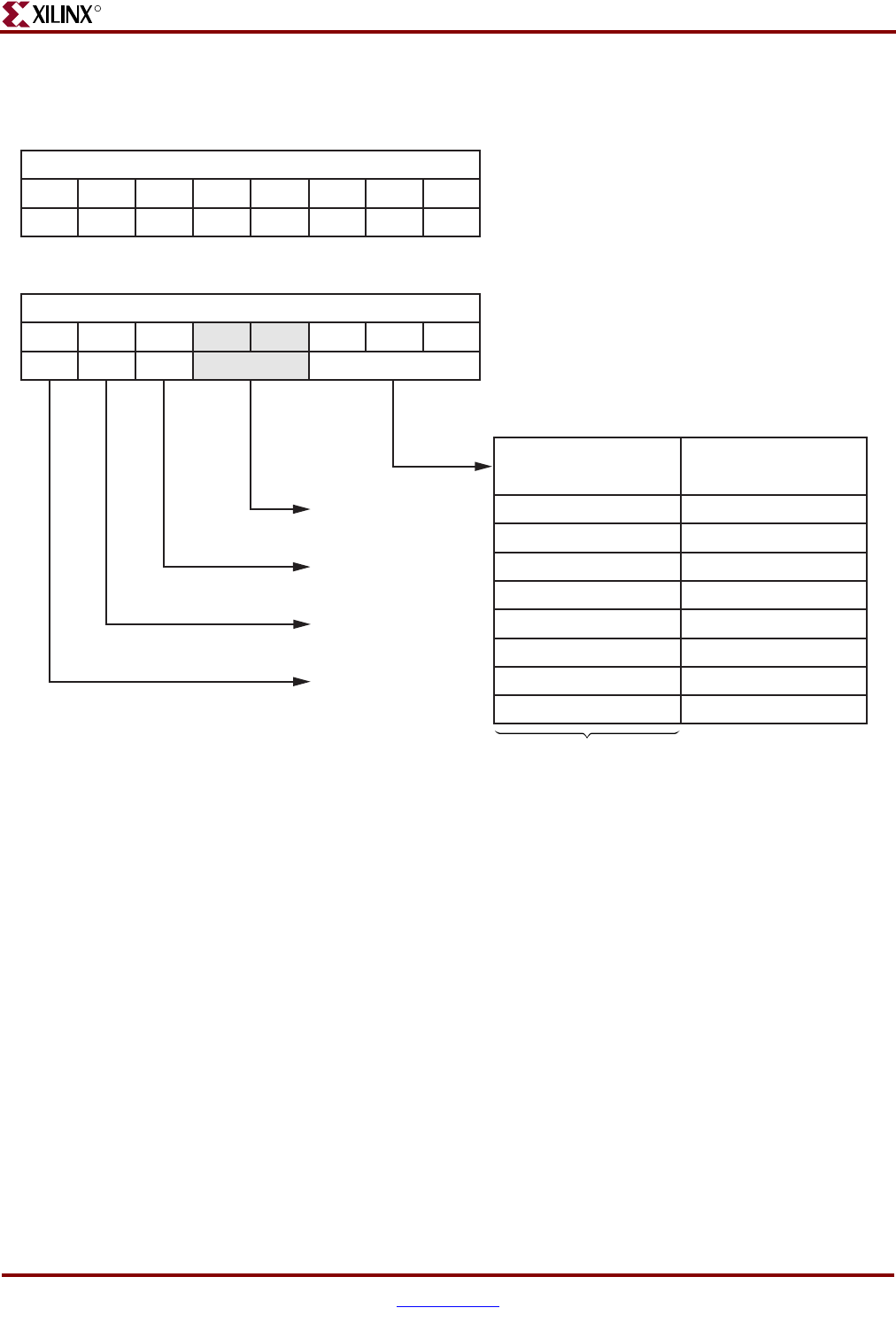

Figure 3-11: DSOCM DCR Registers for Virtex-II Pro

UG018_46_042304

DSARC (DSOCM Address Range Compare Register)

User Programmable Registers

Allocated within DCR address space (Programmer's Model)

8 bits: Address range compare for DSOCM memory space.

They are also configurable via FPGA, through the DSARCVALUE

inputs to the processor block.

Note: The top 8 bits of the CPU address are compared with

DSARC to provide a 16 MB logical address space for DSOCM

block. OCM must be placed in a non-cacheable memory region.

Notes:

1. Reserved bits; will read 0.

2. See section "DSOCM Ports" in the text.

3. DISABLEOPERANDFWD:

When DISABLEOPERANDFWD is asserted, load data from the DSOCM

goes directly into a latch in the processor block. This causes an additional

cycle (a total of two cycles) of latency between a load instruction which

is followed by an instruction that requires the load data as an operand.

When DISABLEOPERANDFWD is not asserted, load data from the DSOCM

must pass through steering logic before arriving at a latch. This causes a

single cycle of latency between a load instruction which is followed by an

instruction that requires the load data as an operand.

4. DSOCMEN:

Enables the DSOCM address decoder.

0

A0/P

1

A1/P

5

A5/P

6

A6/P

7

A7/P

2

A2/P

3

A3/P

4

A4/P

DSCNTL (DCR Control Register)

8 bits: Control Register for DSOCM. They are also configurable v

ia

FPGA, through the DSCNTLVALUE inputs to the processor block.

(P indicates that this bit can be configured during FPGA power up

)

0

D0/P

1

D1/P

5

D5/P...

67

D7/P

2

D2/P

3

D3/P

4

D4/P

DSOCMMCM[0:2]

DSOCMEN

(4)

000

001

010

011

100

101

110

111

2n - 1

N/A

1:1

N/A

2:1

N/A

3:1

N/A

4:1

CPMC405CLOCK:

BRAMDSOCMCLK

Ratio

where n = number of

processor clocks in

one BRAM clock cycle.

Must be an integer.

DISABLEOPERANDFWD

(3)

DSOCMBUSY

(2)

Reserved

(1)