26 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 1: Introduction to the PowerPC 405 Processor

R

Central-Processing Unit

The PowerPC 405 central-processing unit (CPU) implements a 5-stage instruction pipeline

consisting of fetch, decode, execute, write-back, and load write-back stages.

The fetch and decode logic sends a steady flow of instructions to the execute unit. All

instructions are decoded before they are forwarded to the execute unit. Instructions are

queued in the fetch queue if execution stalls. The fetch queue consists of three elements:

two prefetch buffers and a decode buffer. If the prefetch buffers are empty instructions

flow directly to the decode buffer.

Up to two branches are processed simultaneously by the fetch and decode logic. If a branch

cannot be resolved prior to execution, the fetch and decode logic predicts how that branch

is resolved, causing the processor to speculatively fetch instructions from the predicted

path. Branches with negative-address displacements are predicted as taken, as are

branches that do not test the condition register or count register. The default prediction can

be overridden by software at assembly or compile time.

The PowerPC 405 has a single-issue execute unit containing the general-purpose register

file (GPR), arithmetic-logic unit (ALU), and the multiply-accumulate unit (MAC). The

GPRs consist of thirty-two 32-bit registers that are accessed by the execute unit using three

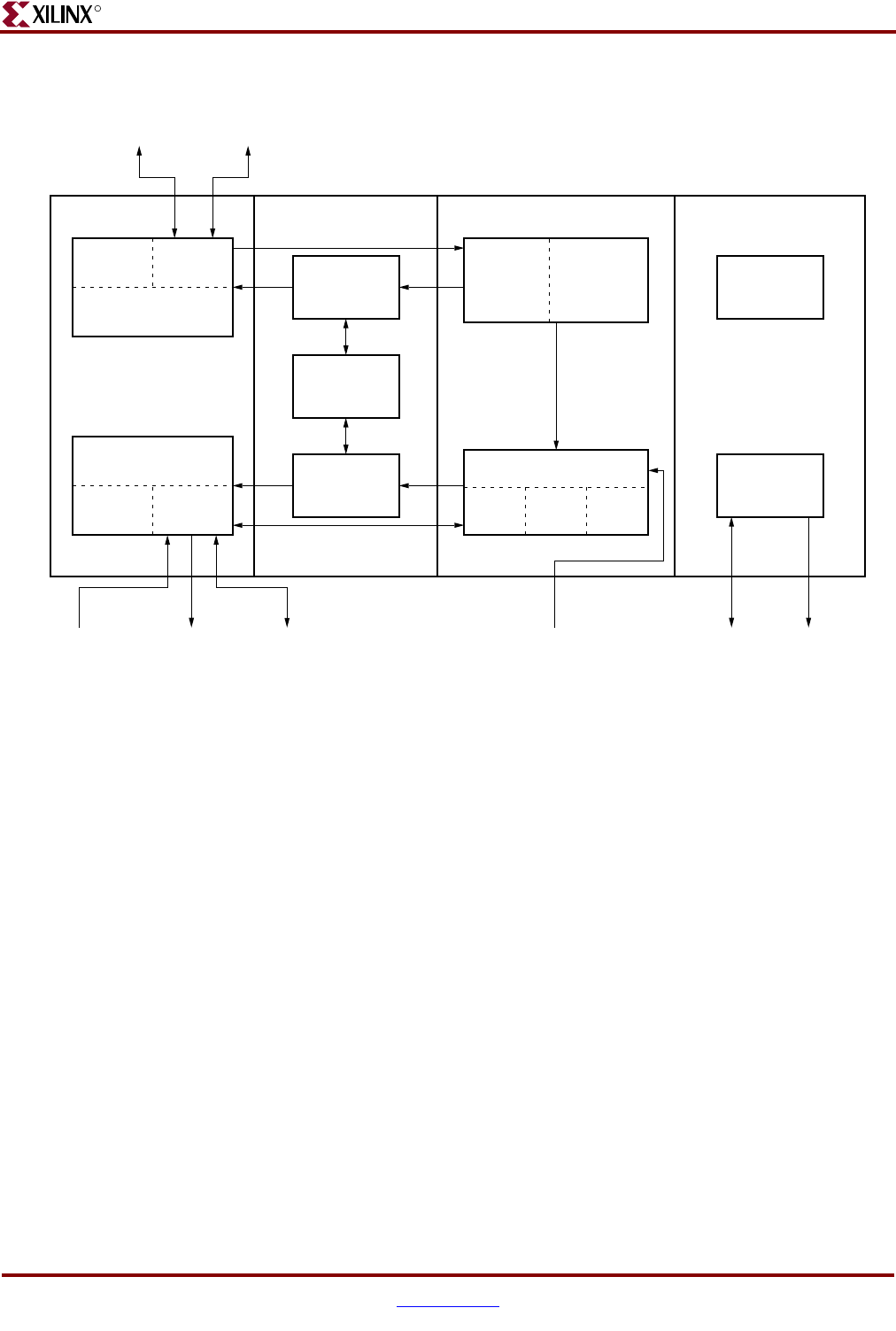

Figure 1-2: PowerPC 405 Organization

a

a. Figure 1-2 is specific to PPC405D5.

UG018_35_102401

I-Cache

Array

I-Cache

Controller

Instruction-Cache

Unit

D-Cache

Array

D-Cache

Controller

Data-Cache

Unit

Instruction

Shadow-TLB

(4-Entry)

Unified TLB

(64-Entry)

Data

Shadow-TLB

(8-Entry)

Execute Unit

32x32

GPR

ALU MAC

3-Element

Fetch Queue

Fetch

and

Decode

Logic

Timers

Debug

Logic

PLB Master

Read Interface

PLB Master

Read Interface

PLB Master

Write Interface

Data

OCM

Instruction

OCM

JTAG

Instruction

Trace

CPUMMU

Timers

and

Debug

Cache Units

External-Interrupt

Controller Interface