186 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 4: PowerPC 405 APU Controller

R

Blocking Instructions

Any non-autonomous instruction that cannot be predictably aborted and later re-issued

must be blocking. During execution of a blocking instruction, all interrupts and exceptions

to the PowerPC are blocked, so as not to prevent it from completing. This is, for example,

true of the

UDI_FCM_Write

instruction if the source of the data is a FIFO inside the FCM. If

aborted after the FIFO pointer has been changed, but before the data has been stored in the

PowerPC register file, such instruction could not be re-issued predictably.

Non-blocking Instructions

Any non-autonomous instruction that can be aborted and predictably re-issued later can

be defined as non-blocking. A non-blocking instruction allows the processor to terminate

the FCM execution, service interrupts and exceptions, and subsequently re-issue the

terminated instruction, with predictable results. If we replace the FIFO in the blocking

example above with a traditional random access memory, the aborted

UDI_FCM_Write

instruction could be predictably re-issued (with no remaining side-effects associated with

a FIFO read pointer).

Instruction Format

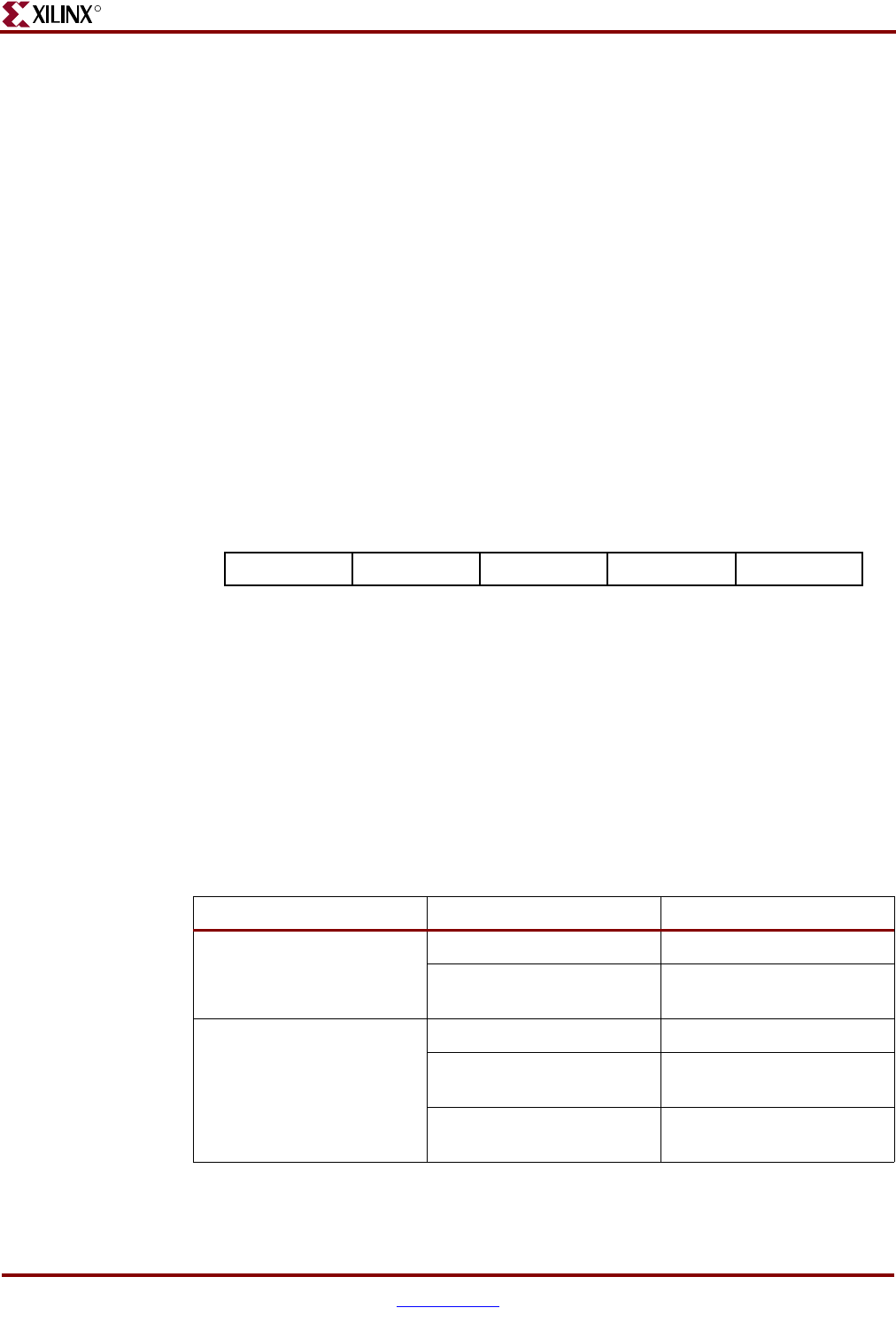

All FCM instructions conform to the general format shown in Figure 4-2.

Generally speaking, the Power PC uses both primary and extended op codes to identify

potential FCM instructions. The op codes are decoded by the APU Controller or the FCM

to identify uniquely the specific FCM instruction. For all pre-defined instructions, the RA

and RB fields specify operand registers, and the RT field the target register. User-defined

instructions (UDI) can be configured to interpret these bit fields as, for instance, immediate

values instead.

The primary and secondary op-codes shown in Table 4-2 can be used as APU instructions:

Figure 4-2: FCM Instruction Format

Table 4-2: APU Op-codes

Primary Op-code Extended Op-code Description

0 (= 0b000000) 0b00000000000 Illegal

all except above Available for UDI

a

that do

not set PPC405(CR) bits

4 (= 0b000100) 0b------1--0- MAcc and Xilinx reserved

0b1----000110 Available for UDIs that

need to set PPC405(CR) bits

all except above Available for UDI’s that do

not set PPC405(CR) bits

Primary Op-code

0611162131

RT RA RB Extended Op-code

UG018_04_2a_051204