202 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 4: PowerPC 405 APU Controller

R

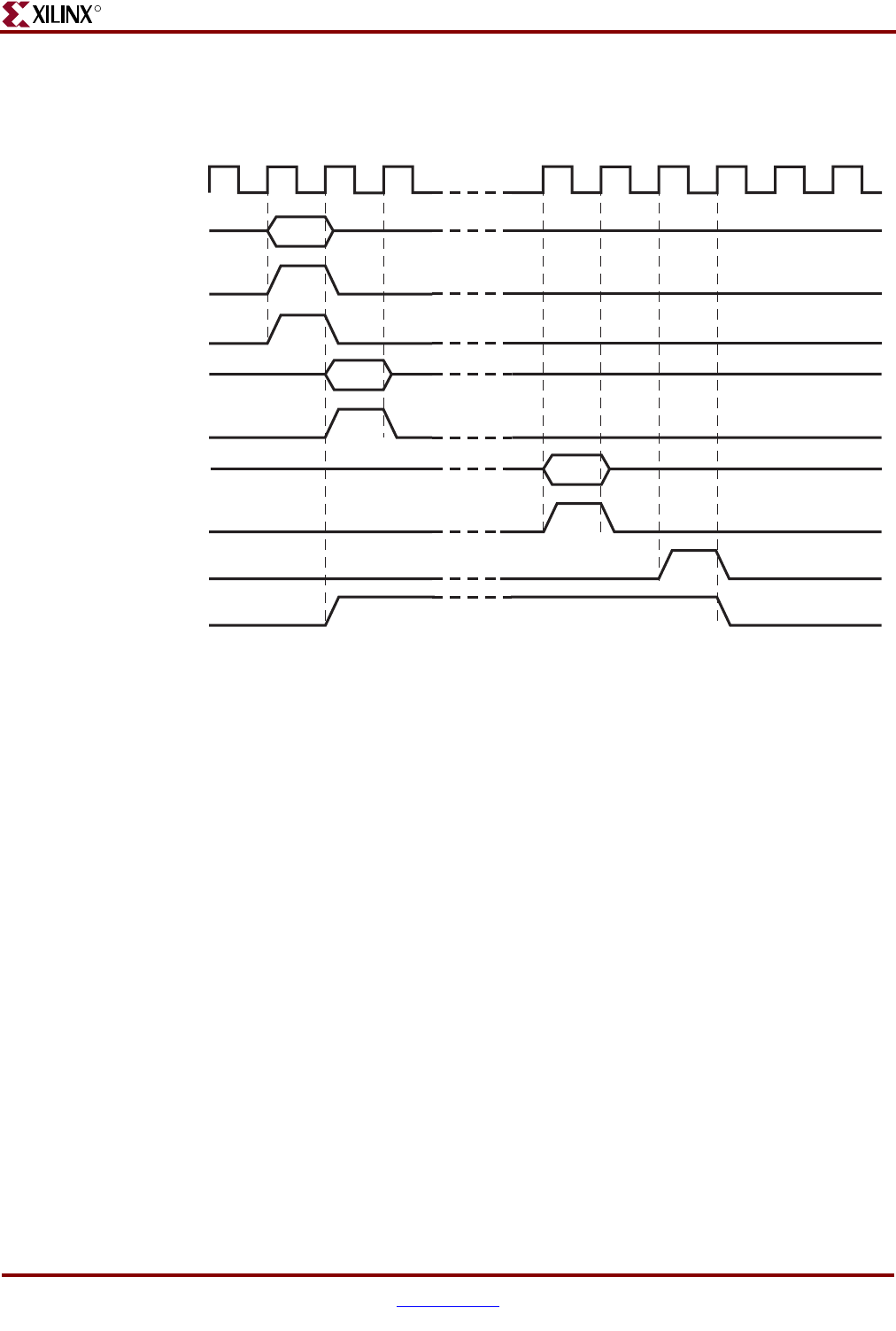

Non-Blocking Transactions

Note: Actual timing results may vary from those shown in Figure 4-6. For example, the operands

could come later than shown.

Figure 4-6: APU Controller Decoded Non-Blocking Transaction Example

UG018_04_05_032504

CPMFCMCLK

APUFCMINSTRUCTION

APUFCMINSTRVALID

APUFCMDECODED

APUFCMRADATA/

APUFCMRBDATA

APUFCMOPERANDVALID

FCMAPURESULT

FCMAPUDONE/

FCMAPURESULTVALID

APUFCMWRITEBACKOK

FCMAPUSLEEPNOTREADY