PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 155

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

ISOCM Output Ports

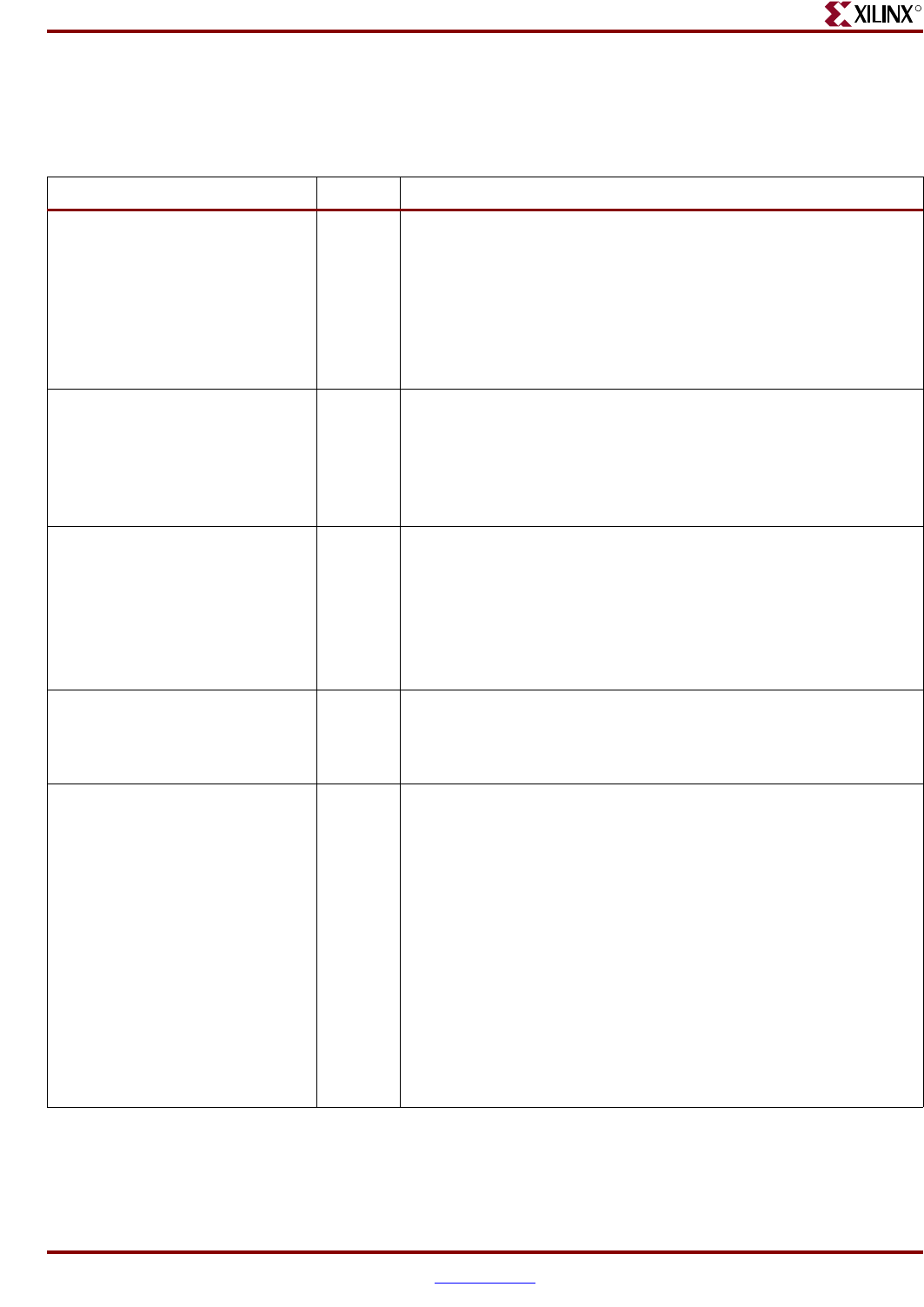

Table 3-8 describes the instruction-side OCM (ISOCM) output ports.

Table 3-8: ISOCM Output Ports

Port Direction Description

ISOCMBRAMEN Output This is a BRAM read enable from the ISOCM controller. This signal

is asserted only for valid ISOCM instruction fetch cycles. For the

fastest memory access applications, the BRAM enable input (EN)

can be locally tied to a logic 1 level. BRAM power consumption can

be reduced by connecting the BRAM enable input (EN) to the

ISOCMBRAMEN signal. If the enable is not tied to a logic 1 level,

a timing analysis must be run to verify that the design meets

frequency of operation requirements.

ISOCMBRAMRDABUS[8:28] Output Read address from ISOCM to BRAM. These 21 outputs correspond

to PPC405 address bits [8:28]. The read address bus is the path for

instruction fetch operations. These 21 address bits corresponds to

internal PPC405 address bits [8:28]. PPC405 address bits [0:7] are

compared against the ISARC register contents, and if a match is

decoded, further steps for instruction fetch are initiated

ISOCMBRAMWRABUS[8:28] Output

Note: Optional. Used in dual-port BRAM interface designs only.

In Virtex-II Pro, this bus provides the write address from the ISOCM

to BRAM via a DCR-based access. The bus value is initially set to the

value stored in the ISINIT register.

In Virtex-4, this bus provides both a read and write address via

DCR-based access. The bus value is initially set to the value stored

in the ISINIT register.

ISOCMBRAMWRDBUS[0:31] Output

Note: Optional. Used in dual-port BRAM interface designs only.

This bus provides 32-bit write data from the ISOCM to BRAM via a

DCR-based access. It is connected to both the even and odd banks of

ISBRAM. It is initially set to the value stored in the ISFILL register.

ISOCMBRAMODDWRITEEN Output

Note: Optional. Used in dual-port BRAM interface designs only.

Write enable to qualify a valid write into a BRAM via a DCR-based

access. This signal enables a write into a memory bank that contains

odd instruction words, that are read back on

BRAMISOCMRDDBUS[32:63].

For Virtex-II Pro, connect this signal to both the Enable (EN) and

Write Enable (WE) inputs of a dual-port ISBRAM port for power

savings.

For Virtex-4, connect ISOCMBRAMODDWRITEEN to the Write

Enable (WE) input of a dual-port BRAM port and

ISOCMDCRBRAMODDEN to the Enable (EN) input of the dual

port ISBRAM.

For single-port ISBRAM implementations, this signal can be left

unconnected.