24 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 1: Introduction to the PowerPC 405 Processor

R

General-Purpose Registers

The processor contains thirty-two 32-bit general-purpose registers (GPRs), identified as r0

through r31. The contents of the GPRs are read from memory using load instructions and

written to memory using store instructions. Computational instructions often read

operands from the GPRs and write their results in GPRs. Other instructions move data

between the GPRs and other registers. GPRs can be accessed by all software.

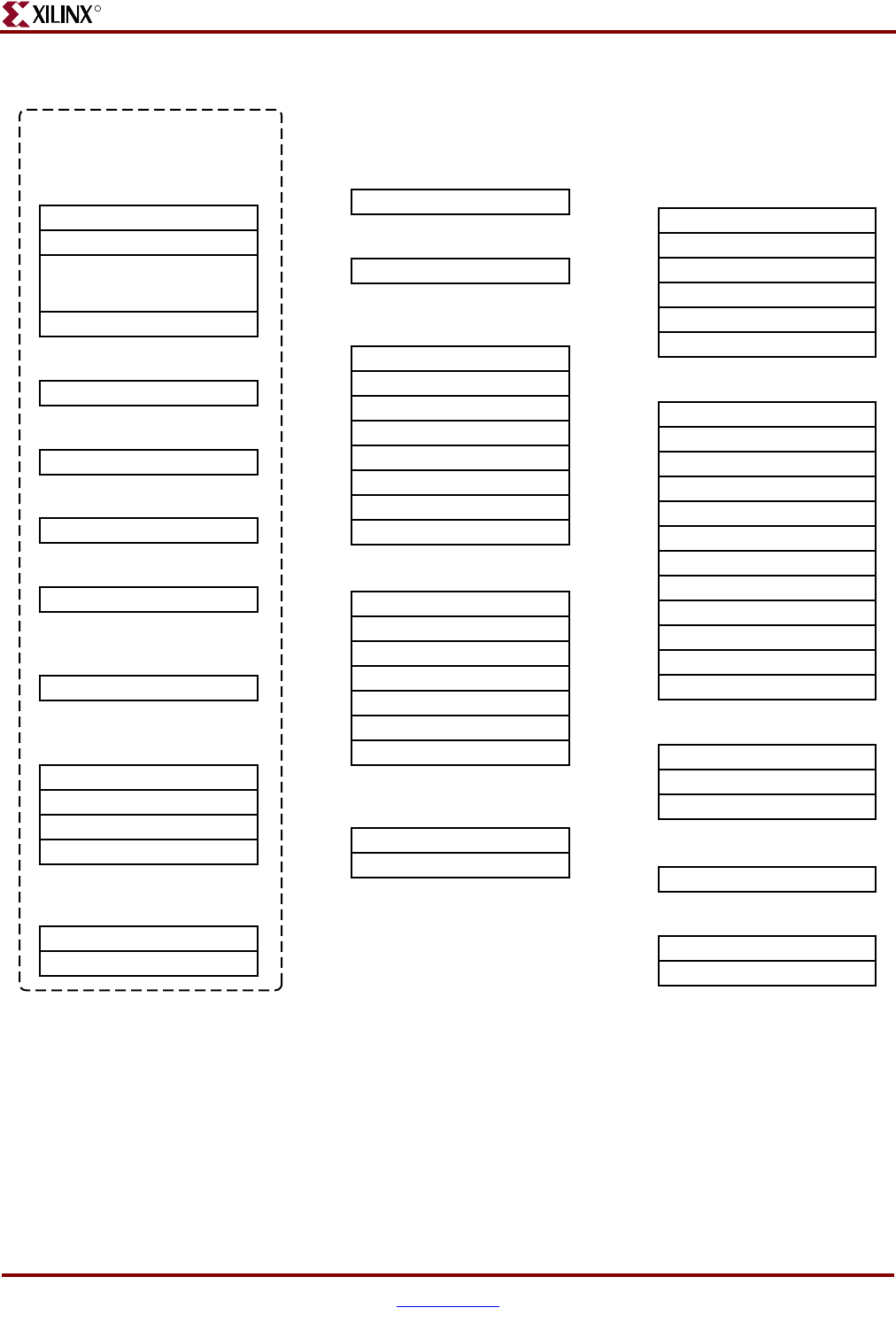

Figure 1-1: PowerPC 405 Registers

UG018_36_102401

MSR

Machine-State Register

CCR0

Core-Configuration Register

SPR General-Purpose

Registers

SPRG0

SPRG1

SPRG2

SPRG3

SPRG4

SPRG5

SPRG6

SPRG7

Memory-Management

Registers

PID

ZPR

Exception-Handling Registers

EVPR

ESR

DEAR

SRR0

SRR1

SRR2

SRR3

Time-Base Registers

TBU

TBL

PVR

Processor-Version Register

Storage-Attribute Control

Registers

DCCR

DCWR

ICCR

SGR

SLER

SU0R

Debug Registers

DBSR

DBCR0

DBCR1

DAC1

DAC2

DVC1

DVC2

IAC1

IAC2

IAC3

IAC4

ICDBR

Timer Registers

TCR

TSR

PIT

Privileged Registers

Time-Base Registers

(read only)

TBU

TBL

USPRG0

User-SPR General-Purpose

Registers

SPR General-Purpose

Registers

(read only)

SPRG4

SPRG5

SPRG6

SPRG7

General-Purpose Registers

r0

.

.

.

r1

r31

CR

Condition Register

CTR

Count Register

LR

Link Register

XER

Fixed-Point Exception Register

User Registers