PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 111

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

EIC Interface I/O Signal Descriptions

The following sections describe the operation of the EIC interface I/O signals.

EICC405CRITINPUTIRQ (Input)

When asserted, this signal indicates the EIC is requesting that the processor block respond

to an external critical interrupt. When deasserted, no request exists. The EIC is responsible

for collecting critical interrupt requests from other peripherals and presenting them as a

single request to the processor block. Once asserted, this signal remains asserted by the EIC

until software deasserts the request (this is typically done by writing to a DCR in the EIC).

EICC405EXTINPUTIRQ (Input)

When asserted, this signal indicates the EIC is requesting that the processor block respond

to an external noncritical interrupt. When deasserted, no request exists. The EIC is

responsible for collecting noncritical interrupt requests from other peripherals and

presenting them as a single request to the processor block. Once asserted, this signal

remains asserted by the EIC until software deasserts the request (this is typically done by

writing to a DCR in the EIC).

PPC405 JTAG Debug Port

The PPC405 core features a JTAG interface to support software debugging. Many

debuggers, such as RISCWatch from IBM, SingleStep from Wind River and the GNU

Debugger (GDB) in the Xilinx Embedded Development Kit (EDK), use the PPC405 JTAG

interface for this purpose.

Like all other signals on the PPC405 core, the user must define the connections from the

JTAG interface to the outside world. Since these connections can only be made through

programmable interconnect, the FPGA must be configured before the PPC405 JTAG

interface is available.

The PPC405 JTAG logic may be connected through the native JTAG port (series

connection) of the FPGA, or directly to programmable I/O (individual connection). The

primary consideration in choosing a connection style is knowing which connection your

software debugger requires.

JTAG Interface I/O Signals

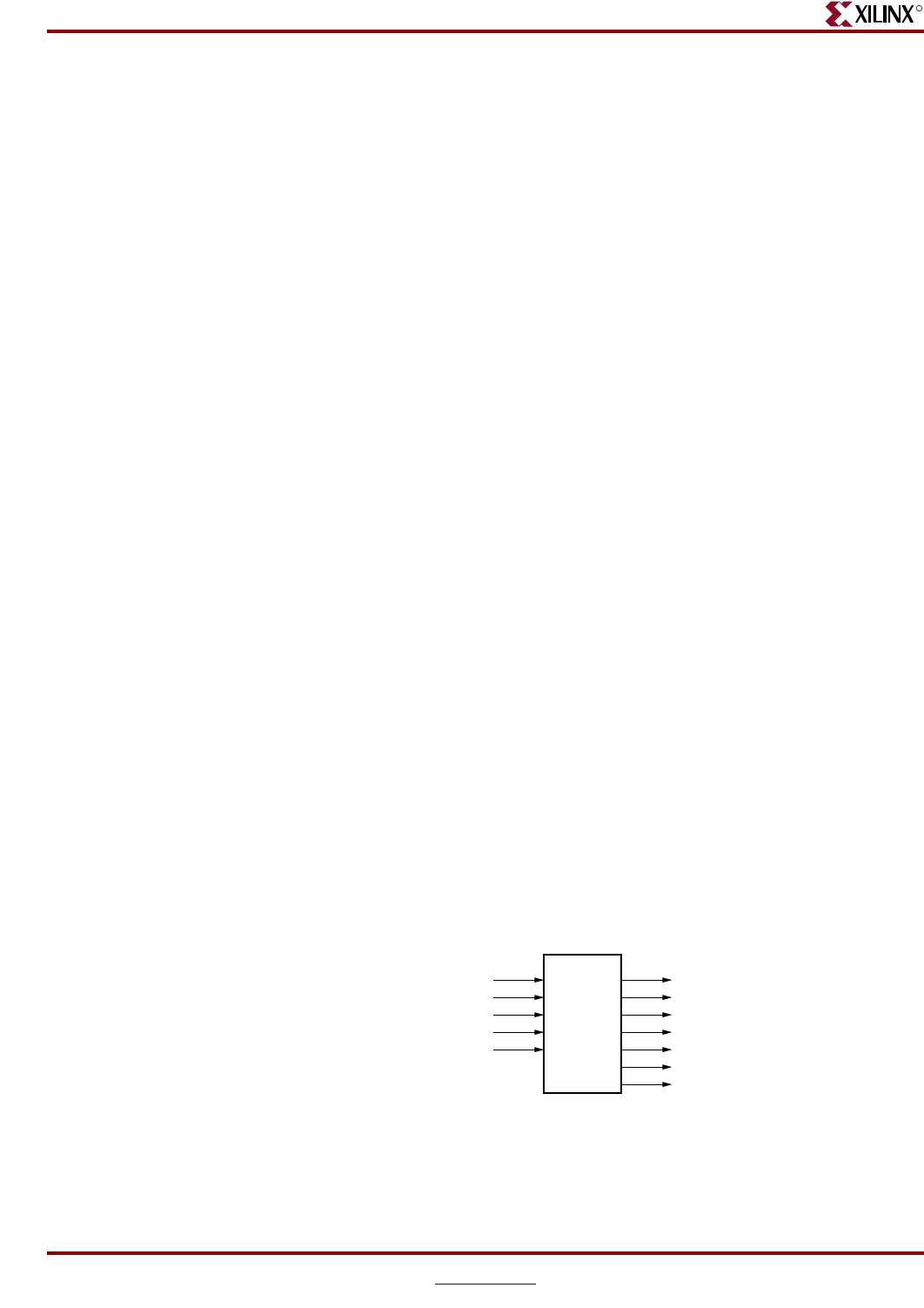

Figure 2-38 shows the block symbol for the JTAG interface.

Figure 2-38: JTAG Interface Block Symbol

UG018_08_102001

PPC405

JTGC405TCK

JTGC405TMS

JTGC405TDI

JTGC405TRSTNEG

JTGC405BNDSCANTDO

C405JTGTDO

C405JTGTDOEN

C405JTGEXTEST

C405JTGCAPTUREDR

C405JTGSHIFTDR

C405JTGUPDATEDR

C405JTGPGMOUT