PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 77

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

Table 2-13 shows the possible values that can be presented by the byte enables and how

they are interpreted by the PLB slave. All encoding of the byte enables not shown are

invalid and are not generated by the DCU. The column headed “32-Bit PLB Slave Data

Bus” assumes an attachment to a 64-bit PLB master as shown in Figure 2-16, above.

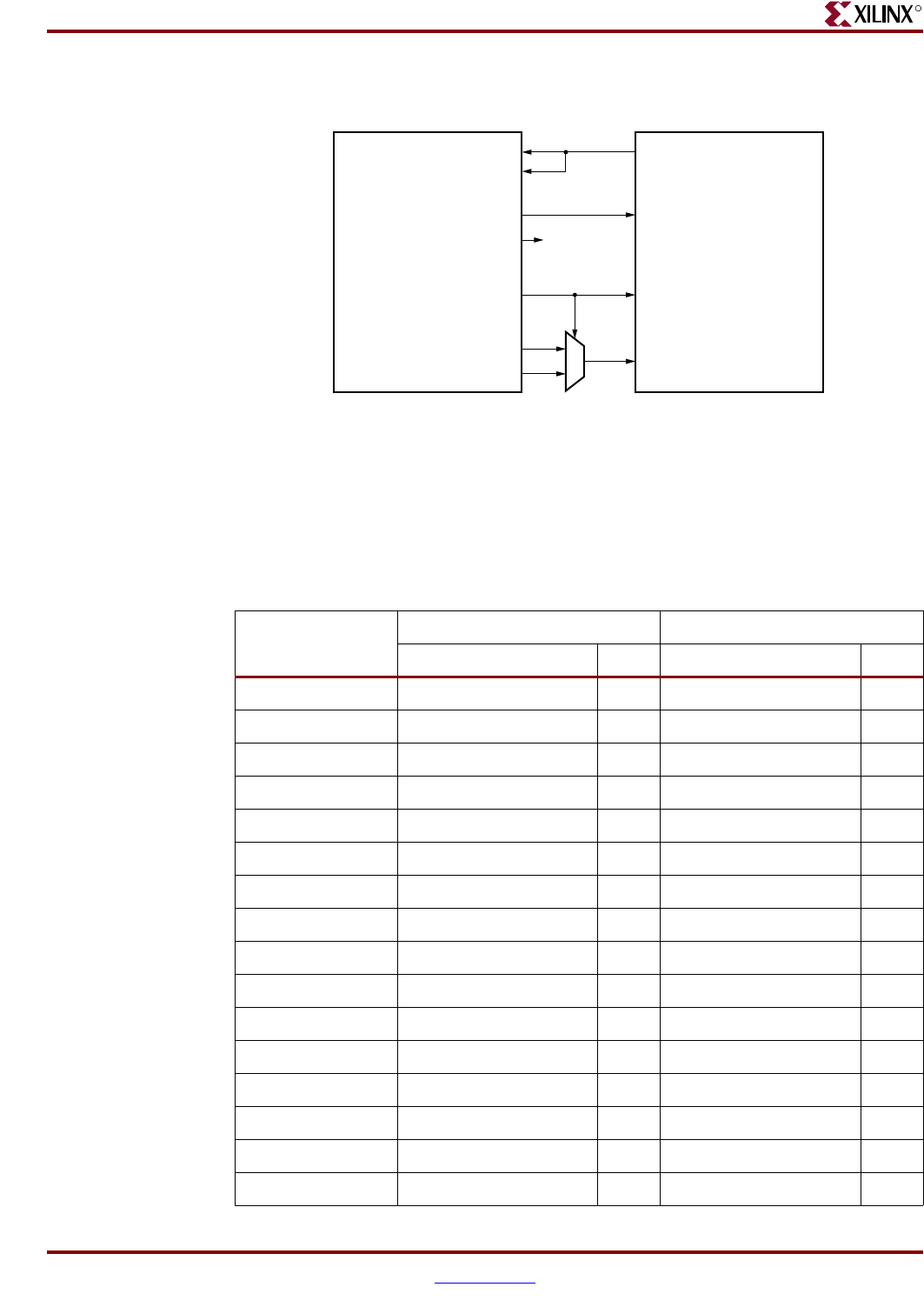

Figure 2-16: Attachment of DSPLB Between 32-Bit Slave and 64-Bit Master

Table 2-13: Interpretation of DCU Byte Enables During Word Transfers

Byte Enables [0:7]

32-Bit PLB Slave Data Bus 64-Bit PLB Slave Data Bus

Valid Bytes Bits Valid Bytes Bits

1000_0000 Byte 0 0:7 Byte 0 0:7

1100_0000 Bytes 0:1 (Halfword 0) 0:15 Bytes 0:1 (Halfword 0) 0:15

1110_0000 Bytes 0:2 0:23 Bytes 0:2 0:23

1111_0000 Bytes 0:3 (Word 0) 0:31 Bytes 0:3 (Word 0) 0:31

0100_0000 Byte 1 8:15 Byte 1 8:15

0110_0000 Bytes 1:2 8:23 Bytes 1:2 8:23

0111_0000 Bytes 1:3 8:31 Bytes 1:3 8:31

0010_0000 Byte 2 16:23 Byte 2 16:23

0011_0000 Bytes 2:3 (Halfword 1) 16:31 Bytes 2:3 (Halfword 1) 16:31

0001_0000 Byte 3 24:31 Byte 3 24:31

0000_1000 Byte 0 0:7 Byte 4 32:39

0000_1100 Bytes 0:1 (Halfword 0) 0:15 Bytes 4:5 (Halfword 2) 32:47

0000_1110 Bytes 0:2 0:23 Bytes 4:6 32:55

0000_1111 Bytes 0:3 (Word 0) 0:31 Bytes 4:7 (Word 1) 32:63

0000_0100 Byte 1 8:15 Byte 5 40:47

0000_0110 Bytes 1:2 8:23 Bytes 5:6 40:55

UG018_20_101501

C405PLBDCUABUS[0:31]

PLBC405DCURDDBUS[0:31]

PLBC405DCURDDBUS[32:63]

C405PLBDCUBE[4:7]

C405PLBDCUBE[0:3]

C405PLBDCUABUS[0:31]

PLBC405DCURDDBUS[0:31]

C405PLBDCUBE[0:3]

C405PLBDCUWRDBUS[32:63]

C405PLBDCUWRDBUS[0:31] C405PLBDCUWRDBUS[0:31]

[29]

64-Bit PLB Master 32-Bit PLB Slave

Unconnected