218 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

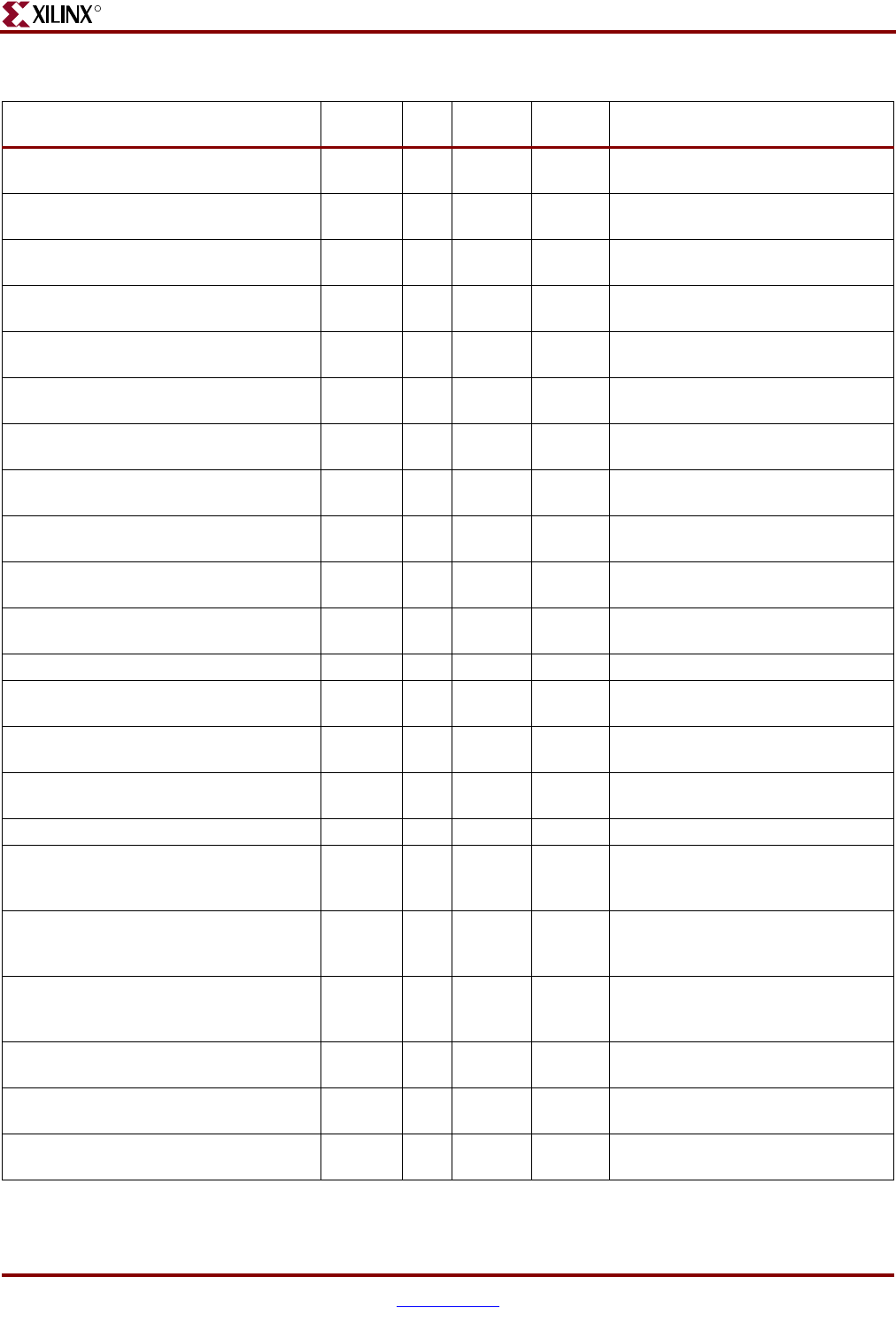

Appendix B: Signal Summary

R

EICC405EXTINPUTIRQ V-II Pro

and V-4

I EIC 0 Indicates an external noncritical

interrupt occurred.

FCMAPUCR[0:3] V-4 I FCM 0 Condition result bits to set in the

PowerPC CR field

FCMAPUDCDCREN V-4 I FCM 0 FCM decoded instruction sets

condition register (CR) bits.

FCMAPUDCDFORCEALIGN V-4 I FCM 0 FCM decoded load/store instruction

with forced word alignment

FCMAPUDCDFORCEBESTEERING V-4 I FCM 0 FCM decoded store instruction will

force Big-Endian steering.

FCMAPUDCDGPRWRITE V-4 I FCM 0 FCM decoded instruction must write

back to the GPR.

FCMAPUDCDLDSTBYTE V-4 I FCM 0 FCM decoded load/store instruction

does byte transfer.

FCMAPUDCDLDSTDW V-4 I FCM 0 FCM decoded load/store instruction

does double word transfer.

FCMAPUDCDLDSTHW V-4 I FCM 0 FCM decoded load/store instruction

does half word transfer.

FCMAPUDCDLDSTQW V-4 I FCM 0 FCM decoded load/store instruction

does quad word transfer.

FCMAPUDCDLDSTWD V-4 I FCM 0 FCM decoded load/store instruction

does word transfer.

FCMAPUDCDLOAD V-4 I FCM 0 FCM decoded load instruction.

FCMAPUDCDPRIVOP V-4 I FCM 0 FCM decoded instruction executes in

privileged mode.

FCMAPUDCDRAEN V-4 I FCM 0 FCM decoded instruction need data

from GPR(Ra).

FCMAPUDCDRBEN V-4 I FCM 0 FCM decoded instruction need data

from GPR(Rb).

FCMAPUDCDSTORE V-4 I FCM 0 FCM decoded store instruction.

FCMAPUDCDTRAPBE V-4 I FCM 0 FCM decoded load/store instruction

will cause alignment exception if the

storage Endian attribute is 1’b0.

FCMAPUDCDTRAPLE V-4 I FCM 0 FCM decoded load/store instruction

will cause alignment exception if the

storage Endian attribute is 1’b1.

FCMAPUDCDUPDATE V-4 I FCM 0 FCM decoded load/store instruction

should update Ra with effective

address.

FCMAPUDCDXERCAEN V-4 I FCM 0 FCM decoded instruction returns carry

status.

FCMAPUDCDXEROVEN V-4 I FCM 0 FCM decoded instruction returns

overflow status.

FCMAPUDECODEBUSY V-4 I FCM 0 Allows FCM to do a multi-cycle

instruction decode

Table B-1: PowerPC 405 Interface Signals in Alphabetical Order (Continued)

Signal

FPGA

Type

a

I/O

Type

Interface

If Unused

Ties To:

b

Function