PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 165

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

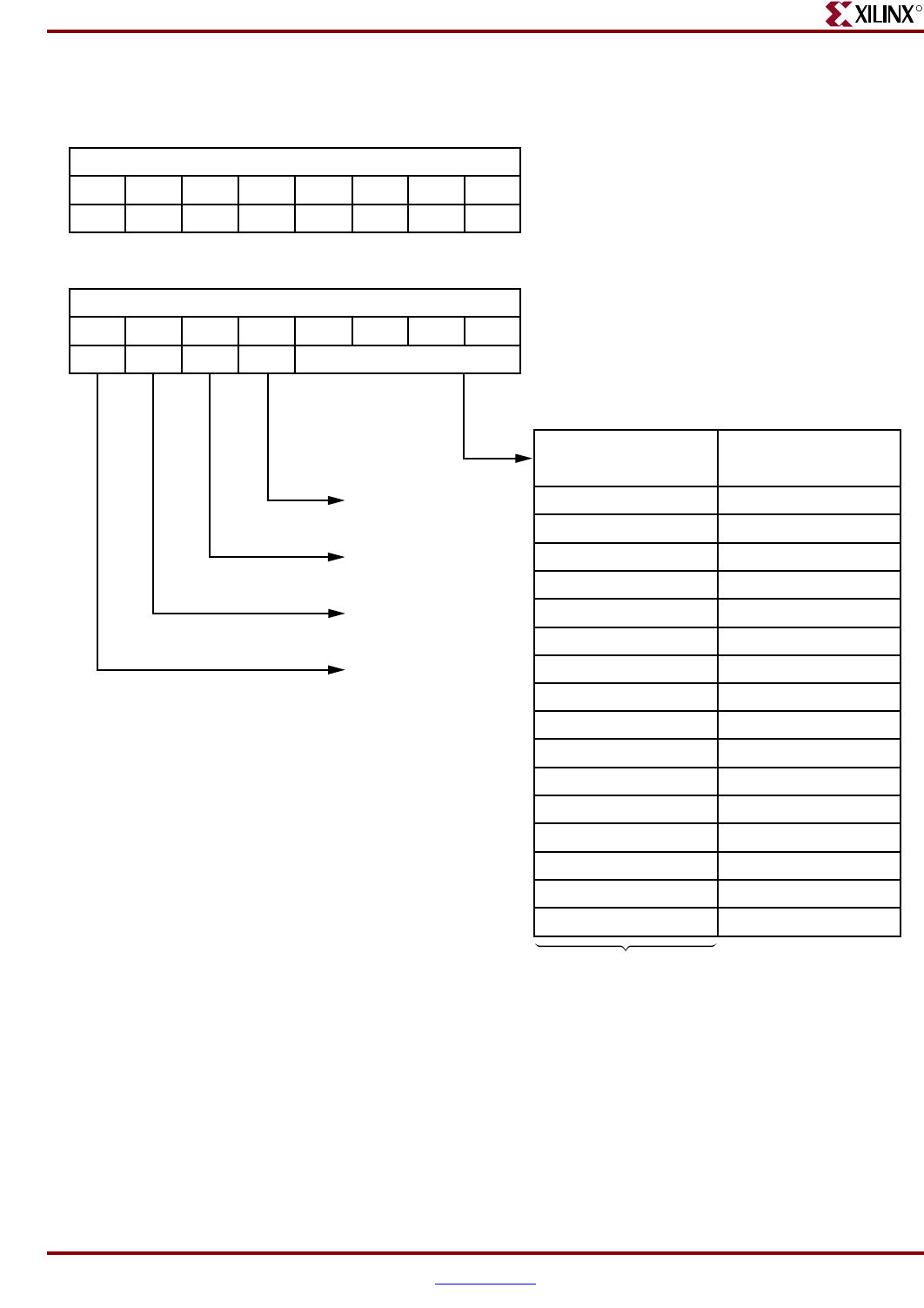

The following section describes the DCR bit mapping during read/write operations on the

ISINIT and ISFILL registers.

Figure 3-14: ISOCM DCR Registers for Virtex-4

UG018_47b_05120

4

ISARC (ISOCM Address Range Compare Register)

User Programmable Registers

Allocated within DCR address space (Programmer's Model)

8 bits: Address range compare for ISOCM memory space.

They are also configurable via FPGA, through the ISARCVALUE

inputs to the processor block.

Note: The top 8 bits of the CPU address are compared with

ISARC to provide a 16 MB logical address space for ISOCM

block. OCM must be placed in a non-cacheable memory region.

Notes:

1. Recommend 1 for auto clock ratio detection. Additionally, when ISOCMMCM

is read back, the value of the auto-detected clock ratio is reflected in terms

of the wait state value.

2. 1 = Enable DCR based readback; this also affects ISINIT readback bit order.

0 = Disable DCR based readback

3. Reserved bits must be configured to 0.

4. ISOCMEN:

Enables the ISOCM address decoder.

0

A0/P

1

A1/P

5

A5/P

6

A6/P

7

A7/P

2

A2/P

3

A3/P

4

A4/P

ISCNTL (ISOCM Control Register)

8 bits: Control Register for ISOCM. They are also configurable v

ia

FPGA, through the ISCNTLVALUE inputs to the processor block

.

Legacy support for backward compatibility with Virtex-II Pro

0

D0/P

1

D1/P...

5

. . .

[4:7] wait state register

67

D7/P

2

D2/P

3

D3/P

4

D4/P

ISOCMMCM[0:3]

ISOCMEN

(4)

0000

0001

0010

0011

0100

0101

0110

0111

2n - 1

Not supported

1:1

Not supported

2:1

Not supported

3:1

Not supported

4:1

CPMC405CLOCK:

BRAMDSOCMCLK

Ratio

1000

1001

1010

1011

1100

1101

1110

1111

Not supported

5:1

Not supported

6:1

Not supported

7:1

Not supported

8:1

where n = number of

processor clocks in

one OCM clock cycle.

Must be an integer.

Reserved

(3)

Enable DCR based readback

(2)

Auto clock ratio detection

(1)