PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 185

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

has a configurable format and is a true extension of the PowerPC instruction set

architecture (ISA).

Enabling the APU Controller

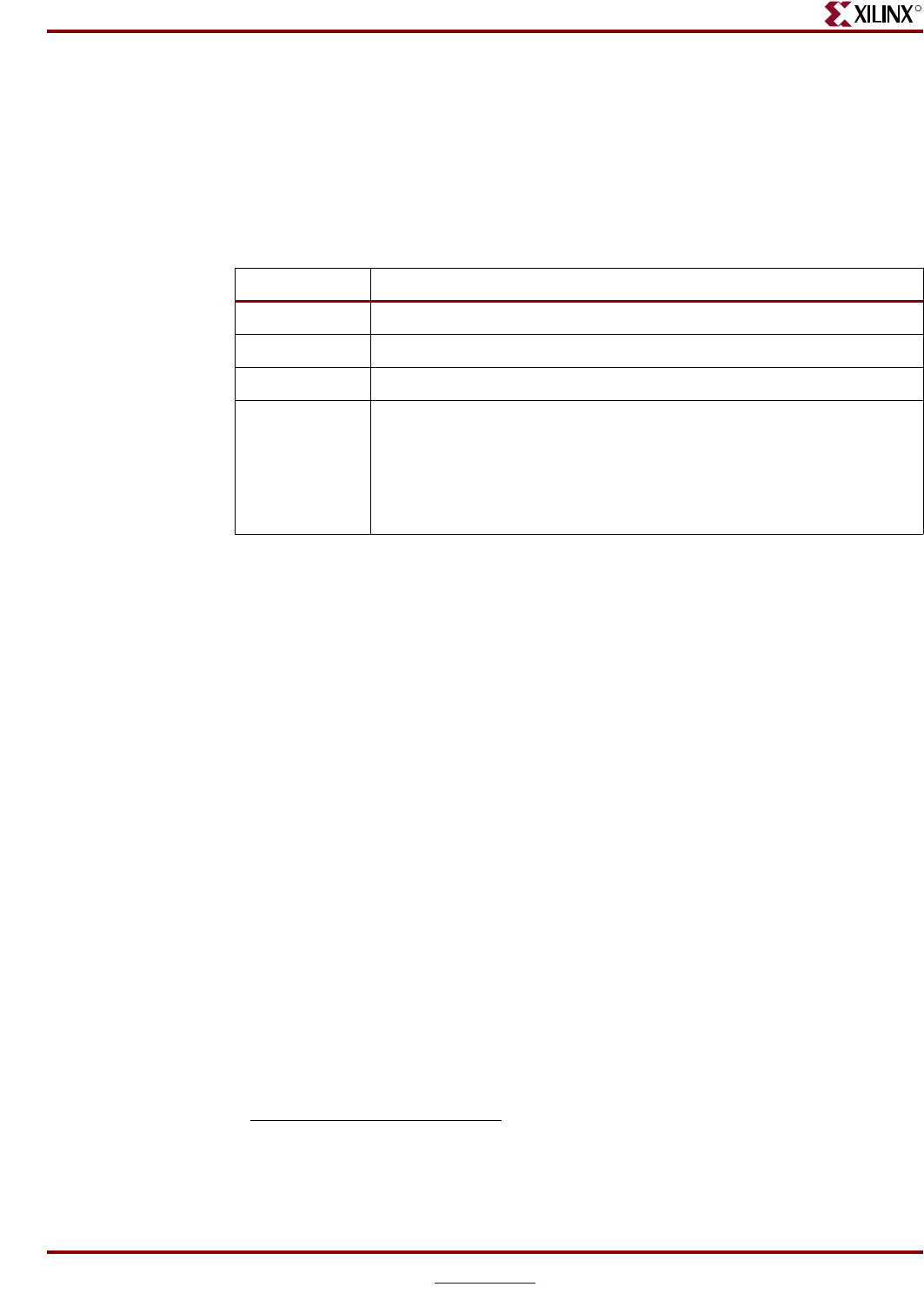

The PowerPC MSR register must be configured before the processor can use the APU

controller. Table 4-1 describes the APU controller-related bits in the MSR.

Instruction Classes

The ISA extensions to the PowerPC are defined by their interaction with the normal

processor pipeline execution. This leads to three different instruction classes: autonomous,

non-autonomous blocking, and non-autonomous non-blocking.

Autonomous Instructions

Instructions in the autonomous class do not stall the pipeline of the PowerPC. They are

typically fire-and-forget type instructions that are not expected to return any state (for

example, overflow) or data to the processor pipeline. An example is a user-defined

UDI_FCM_Read instruction

(1)

, where an FCM register is loaded with the contents of one of

the PowerPC GPR registers without returning any data to the processor. Although

autonomous instructions do not stall execution of native instructions, they can stall

execution of subsequent FCM instructions in case the FCM is not done with an earlier

instruction.

Non-autonomous Instructions

A non-autonomous instruction will stall normal instruction execution in the PowerPC

pipeline until the FCM instruction is done. This is typical for instructions that are expected

to return some state (e.g. overflow) or data to the PowerPC. For example a user-defined

UDI_FCM_Write instruction that takes data from the FCM and writes it to a PowerPC

GPR location.

Table 4-1: APU Controller-Related MSR Bits

Bit(s) in MSR Description

6 APU present (1=true, 0=false)

12 Enable APU exception (1=true, 0=false)

18 FCM floating point unit present (1=true, 0=false)

(20,23) Floating point exception mode (FE0,FE1):

x (0,0) Ignore FP exceptions

x (1,0) Imprecise recoverable mode

x (0,1) Imprecise non-recoverable mode

x (1,1) Precise mode

1. Note that this would not be the same as the “Load” instructions that operate on the storage hierarchy, such as

caches, OCM, or PLB.