PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 187

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

Instruction Decoding

FCM instructions can be decoded either by the APU Controller or by the FCM itself.

APU Controller decoding benefits from the higher clock frequencies possible inside the

hard core. This results in a minimum of latency overhead in the decode stage, improving

overall performance. The APU Controller can decode two types of FCM instructions: pre-

defined instructions that are hard coded in the APU Controller and a limited number of

user-defined instructions.

FCM decoding, although slower than its counterpart, allows many more user-defined

instructions to be implemented.

APU Controller Pre-Defined Instruction Decoding

Two types of pre-defined instructions can be decoded by the APU Controller: Floating

point and FCM Load/Store.

Floating Point Instructions

The APU Controller can be enabled to decode all PowerPC floating-point instructions. In

addition to this, three groups of floating point instructions can be selectively disabled: the

complex arithmetic, conversion, and estimates groups.

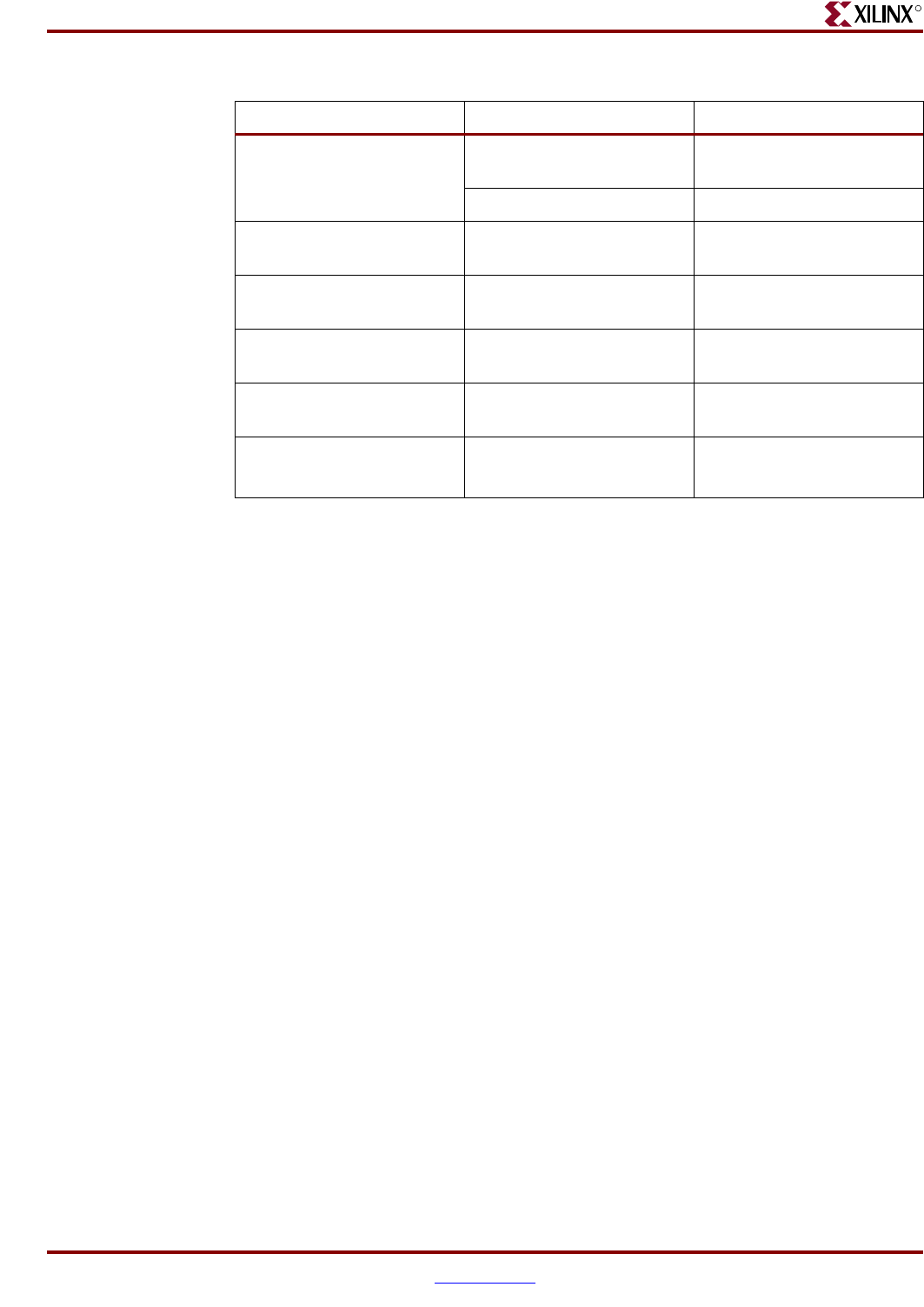

31 (= 0b011111) 0b-----001110 Pre-defined FCM

Load/Store

0b-111-010-1- FCM integer divide

(= 0b110---)

b

0b----------- Pre-defined FPU

Load/Store

32 (= 0b011111) 0b1----1-111- Pre-defined FPU

Load/Store

59 (= 0b111011) 0b----------- Pre-defined PowerPC FPU

instructions

62 (= 0b111110) 0b--------1-- Pre-defined FPU

Load/Store

63 (= 0b111111) 0b---------- Pre-defined PowerPC FPU

instructions

a. User-defined Instruction. For details refer to the “APU Controller User-Defined Instruction Decoding”

section of this chapter.

b. In this case, the first three bits are defined and the last three will change depending on the FPU

instruction.

Table 4-2: APU Op-codes (Continued)

Primary Op-code Extended Op-code Description