PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 197

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

APU Controller Attributes

The following input signals are used as reset values for the APU Controller configuration

registers. The reset values can be over-written using DCR. For details see the “APU

Controller Configuration” section in this chapter.

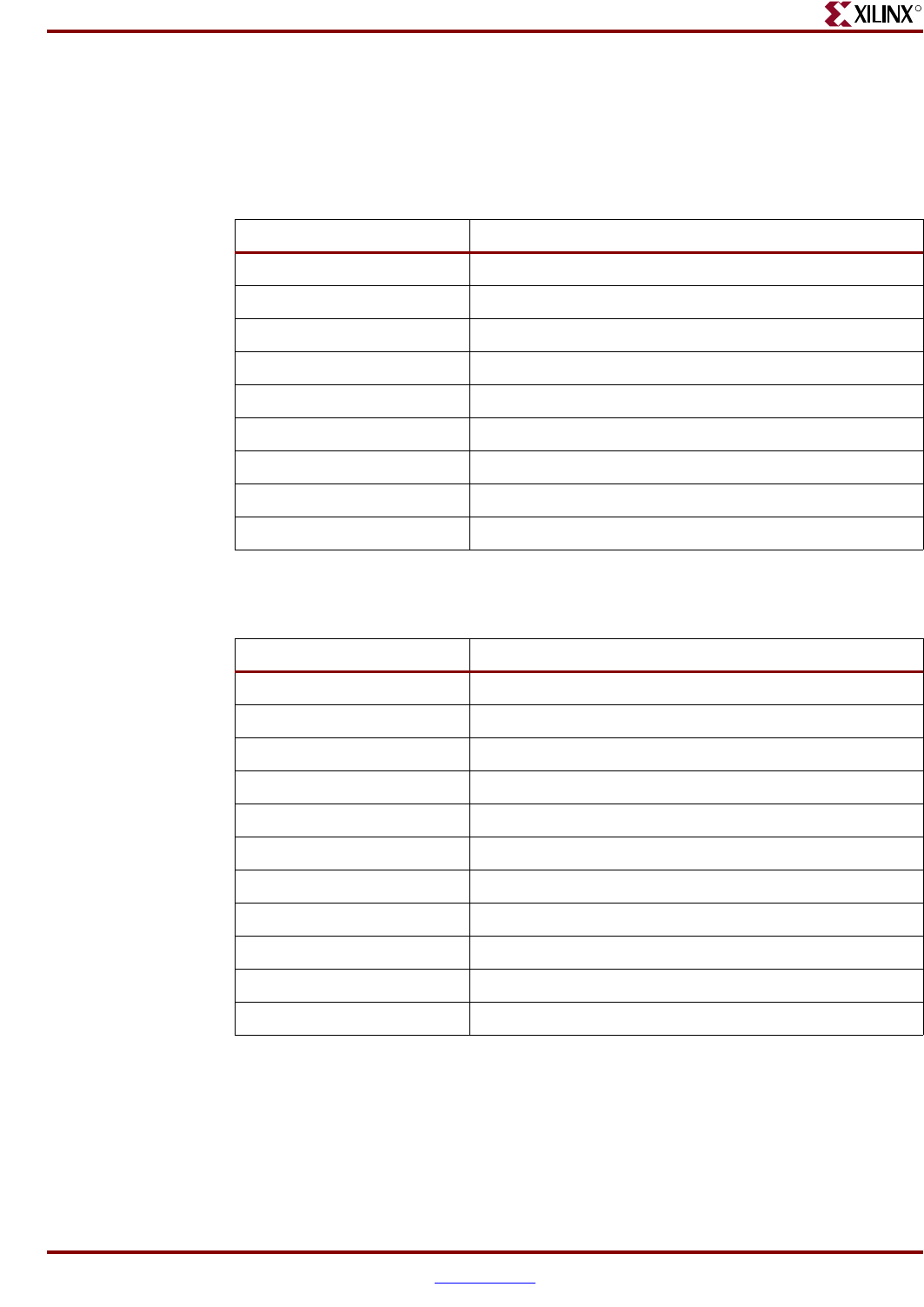

Table 4-8: APU Controller Attributes

Attribute Signal Function

TIEAPUUDI1[0:23] Reset value for UDI register 1.

TIEAPUUDI2[0:23] Reset value for UDI register 2.

TIEAPUUDI3[0:23] Reset value for UDI register 3.

TIEAPUUDI4[0:23] Reset value for UDI register 4.

TIEAPUUDI5[0:23] Reset value for UDI register 5.

TIEAPUUDI6[0:23] Reset value for UDI register 6.

TIEAPUUDI7[0:23] Reset value for UDI register 7.

TIEAPUUDI8[0:23] Reset value for UDI register 8.

TIEAPUCONTROL[0:15] Reset values for the APU control register.

Table 4-9: Bit Map Between TIEAPUUDIn and UDI Configuration Registers

UDI Configuration Field TIEAPUUDI Bits

PriOpCodeSel 0

ExtOpCode (1:11)

PrivOp 12

RaEn 13

RbEn 14

GPRWrite 15

XerOVEn 16

XerCAEn 17

CRFieldEn (18:20)

Type (21:22)

UDIEn 23