140 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 3: PowerPC 405 OCM Controller

R

Comparison of Virtex-II Pro and Virtex-4 OCM Controllers

The Virtex-4 OCM controller is completely backward compatible with the Virtex-II Pro

OCM controller. Table 3-1 highlights the new features available only on the Virtex-4 OCM

controller. Detailed discussion of these features will be provided later in this chapter.

Functional Features

Common Features for DSOCM and ISOCM

x Separate instruction and data memory interface between the processor block and

BRAMs in the FPGA. Eliminates processor local bus (PLB) arbitration between

instruction- and data-side interfaces to external memory.

x Dedicated interface to the Device Control Register (DCR) bus for the ISOCM and

DSOCM controllers. Dedicated DCR bus loop inside the processor block for the OCM

controllers.

x FPGA-configurable DCR register addresses within the DSOCM and ISOCM

controllers.

x Independent 16 MB logical memory space available within PPC405 memory map for

each of the DSOCM and ISOCM controllers.

x Multi-cycle mode option for instruction-side and data-side interfaces. Multi-cycle

operation uses an N:1 processor-to-BRAM clock ratio.

i For Virtex-II Pro, N is an integer from 1 through 4.

i For Virtex-4, N is an integer from 1 through 8.

x Virtex-4 only: Optional auto clock ratio detection to eliminate the need for

programming the control registers of the CPU-to-BRAM clock ratio. This feature

simplifies the programming model to use DSOCM and ISOCM.

Features for Data-Side OCM (DSOCM)

x 32-bit Data Read bus and 32-bit Data Write bus.

x Byte write access to DSBRAM support.

x Second port of dual port DSBRAM is available to read/write from an FPGA interface.

x 22-bit address to DSBRAM port.

x DCR Registers: DSCNTL, DSARC.

x Virtex-4 only: Optional support for variable latency for read or write data transfer.

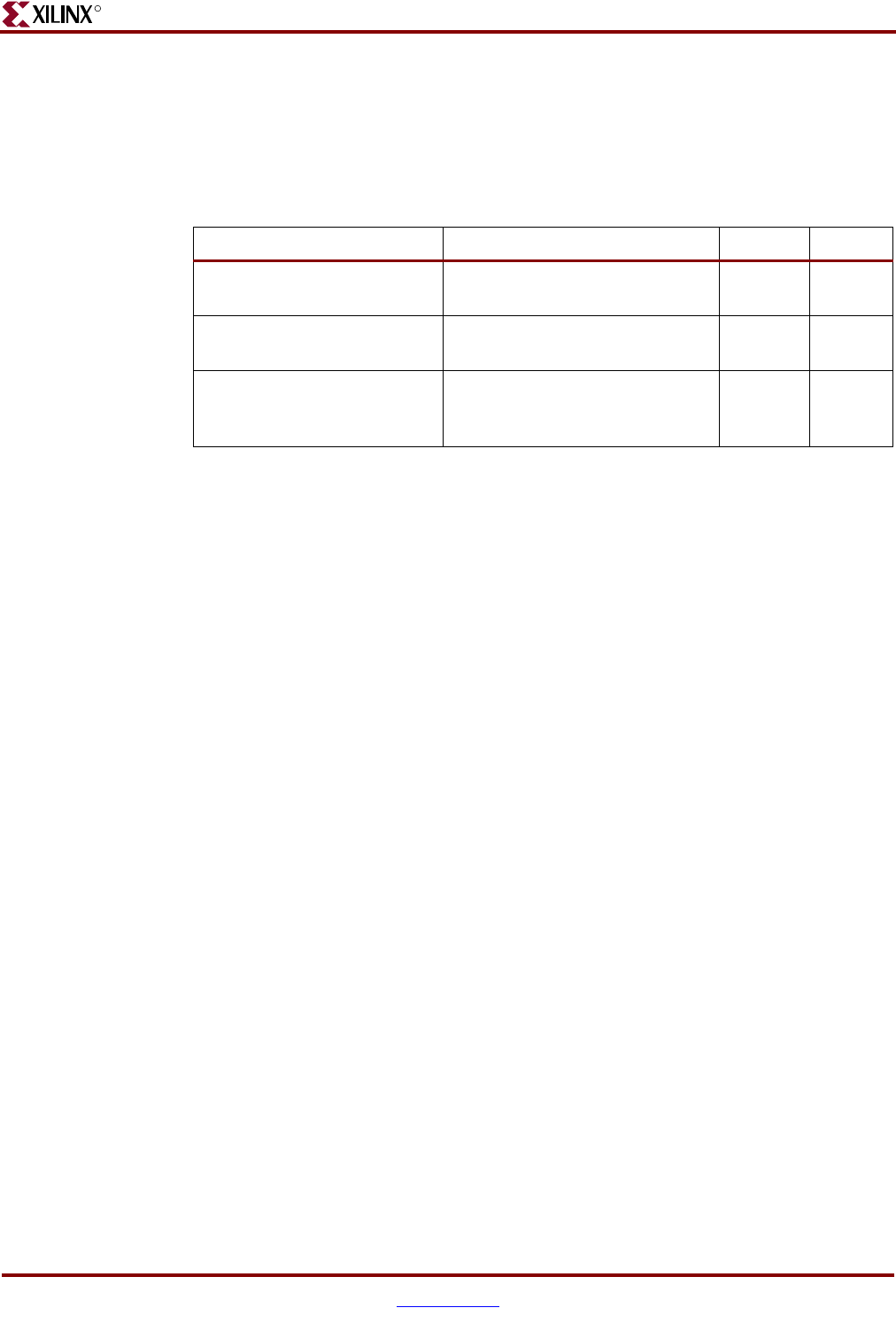

Table 3-1: Features Introduced in Virtex-4 OCM

Feature Primary Advantage ISOCM DSOCM

Variable latency for read and

write access to DSOCM

Wide range of new applications

utilizing memory-mapped I/O

N/A Yes

DCR-based read access to

ISOCM.

Support software debugging for

ISOCM.

Yes N/A

Auto clock ratio detection

and enhanced clocking

support.

Eliminate the need to load wait

state register using software. Up

to 8:1 clock ratio supported.

Yes Yes