50 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 2: Input/Output Interfaces

R

x The prefetch address does not fall outside the current 1 KB physical page.

Address pipelining of cacheable prefetch requests can occur if all of the following

conditions are met:

x Address pipelining is supported by the PLB slave.

x The ICU is not already involved in an address-pipelined PLB transfer.

x A branch or interrupt does not modify the sequential execution of the current (first)

instruction-fetch request.

x Cacheable prefetching is enabled (CCR0[PFC] 1).

x A cacheable instruction-prefetch is requested, and the instruction is not in the

instruction cache, the fill buffer, or being returned over the ISOCM interface.

x The prefetch address does not fall outside the current 1 KB physical page.

Guarded Storage

Accesses to guarded storage are not indicated by the ISPLB interface. This is because the

PowerPC Architecture allows instruction prefetching when:

x The processor is in real mode (instruction address translation is disabled).

x The fetched instruction is located in the same physical page (1 KB) as an instruction

that is required by the sequential execution model.

x The fetched instruction is located in the next physical page (1 KB) as an instruction

that is required by the sequential execution model.

Memory should be organized such that real-mode instruction prefetching from the same

or next 1 KB page does not affect sensitive addresses, such as memory-mapped I/O

devices.

If the processor is in virtual mode, an attempt to prefetch from guarded storage causes an

instruction-storage interrupt. In this case, the prefetch never appears on the ISPLB.

Instruction-Side PLB I/O Signal Table

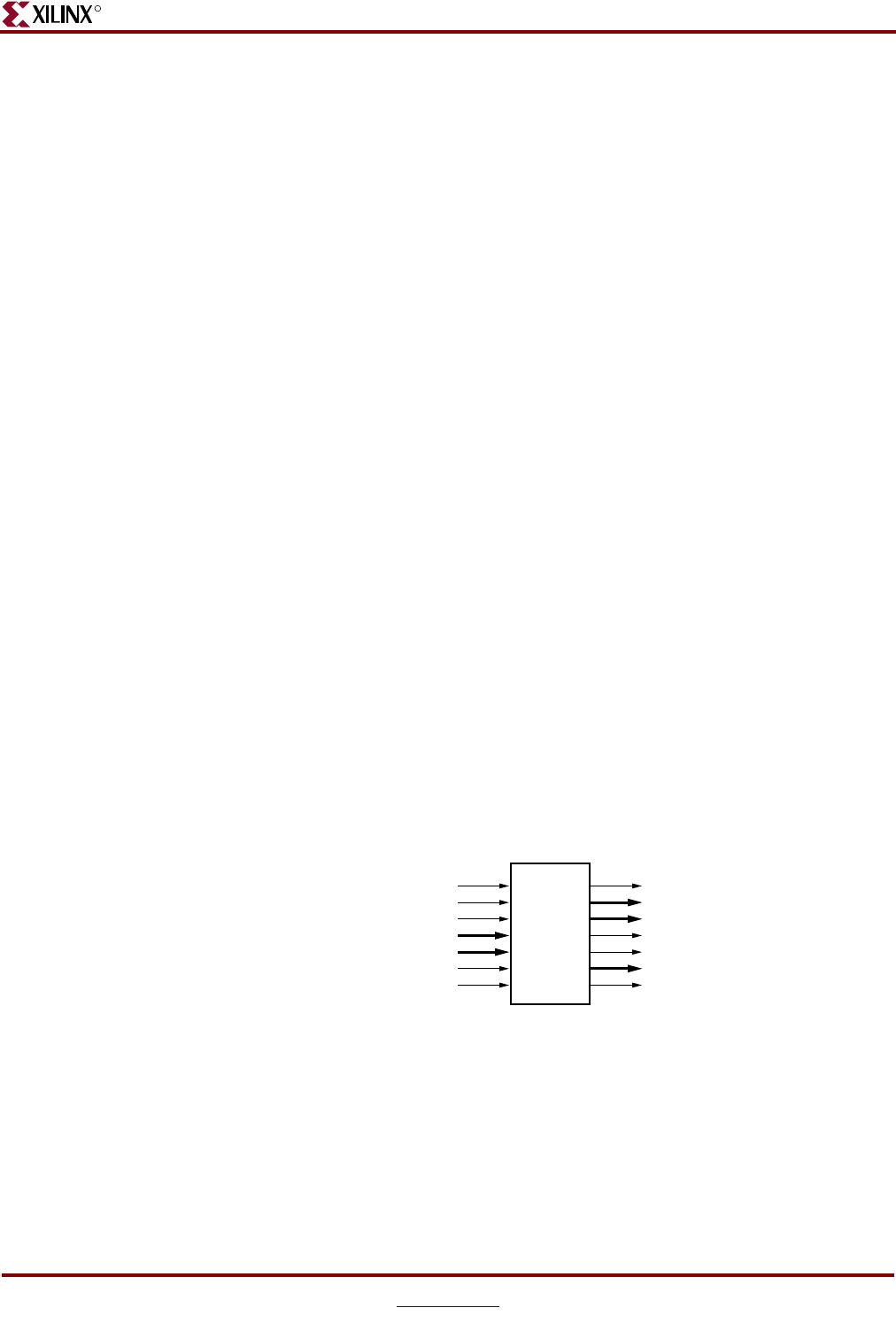

Figure 2-4 shows the block symbol for the instruction-side PLB interface. The signals are

summarized in Table 2-7.

Figure 2-4: Instruction-Side PLB Interface Block Symbol

UG018_04_051204

PPC405

PLBC405ICUADDRACK

PLBC405ICUSSIZE1

PLBC405ICURDDACK

PLBC405ICURDDBUS[0:63]

PLBC405ICURDWDADDR[1:3]

PLBC405ICUBUSY

PLBC405ICUERR

C405PLBICUREQUEST

C405PLBICUABUS[0:29]

C405PLBICUSIZE[2:3]

C405PLBICUCACHEABLE

C405PLBICUU0ATTR

C405PLBICUPRIORITY[0:1]

C405PLBICUABORT