192 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 4: PowerPC 405 APU Controller

R

UDI Configuration Registers

The APU Controller includes eight UDI configuration registers. This allows the user to

define as many custom instructions and have them decoded in the fast APU Controller,

rather than out in the slower FCM. The 32-bit-wide registers define the PowerPC related

behavior of the UDI execution. The individual bits are described in Table 4-5.

ForceAlign 20 Force word alignment for FCM Load/Store data.

Forces two least significant address bits to 0.

LETrap 21 Enable little-endian Traps for FCM Load/Store. If

FCM expects big-endian and the accessed memory is

little-endian (APUFCMENDIAN=1), an alignment

exception will be cast.

BETrap 22 Enable big-endian Traps for FCM Load/Store. If

FCM expects little-endian and the accessed memory

is big-endian (APUFCMENDIAN=0), an alignment

exception will be cast.

BESteer 23 Forces big-endian steering of FCMAPURESULT for

FCM Store. PowerPC internally byte-flips little-

endian results.

APUDiv 24 Perform PPC integer divide operations in FCM.

- (25:30) Not used.

FCMEn 31 Enable FCM usage.

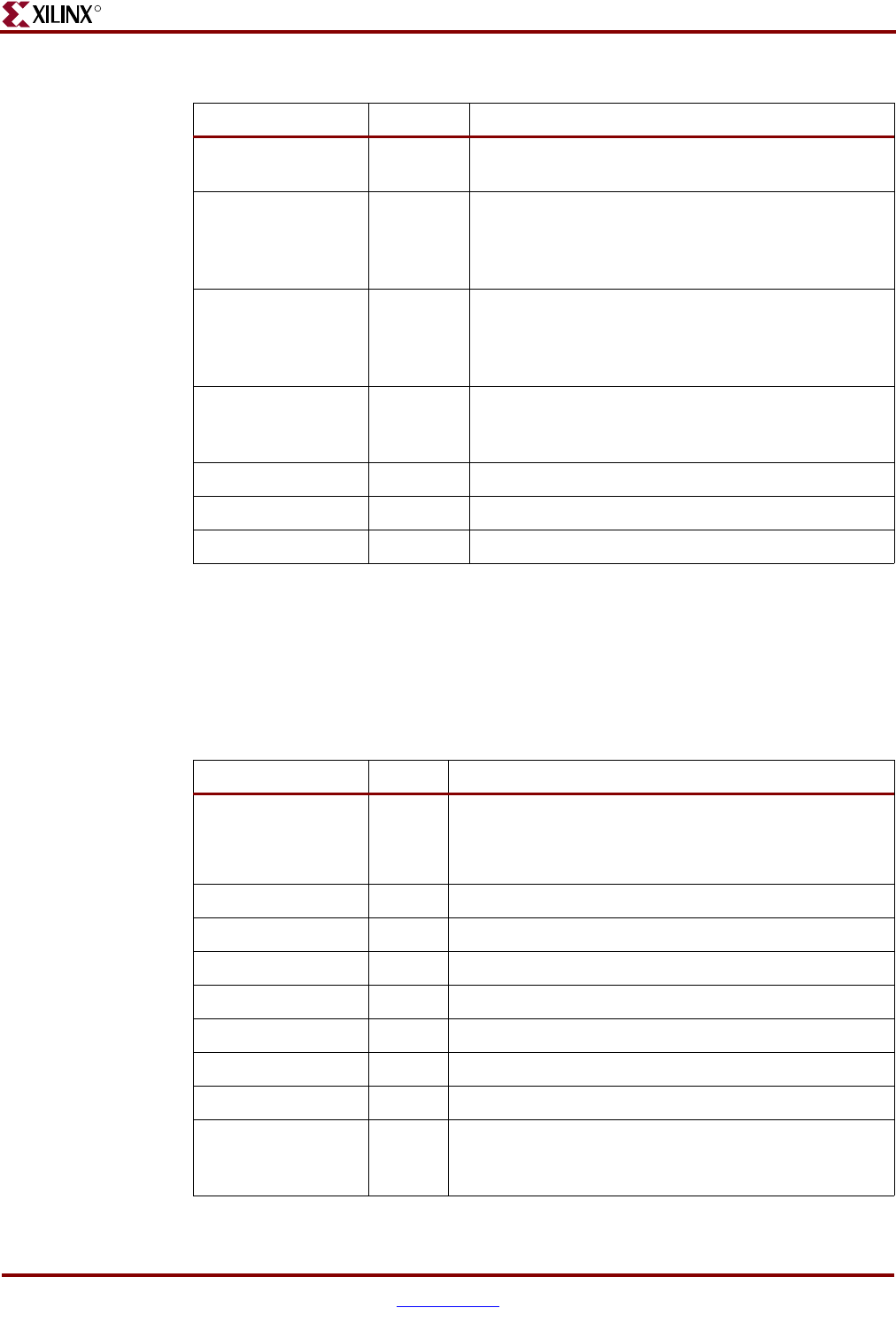

Table 4-4: APU Controller Configuration Register Bit Description (Continued)

Name Bit Description

Table 4-5: UDI Configuration Register Bit Description

Name Bit Description

PriOpCodeSel 0 Select primary op-code for instruction:

0b0 select 0 (= 0b000000)

0b1 select 4 (= 0b000100)

ExtOpCode (1:11) Extended op-code of instruction.

PrivOp 12 Execute only in priviliged mode.

RaEn 13 Requires operand from GPR(RA).

RbEn 14 Requires operand from GPR(RB).

GPRWrite 15 Write back result to GPR(RT) .

XerOVEn 16 Enable return of overflow status.

XerCAEn 17 Enable return of carry status.

CRFieldEn (18:20) Select which field in the PowerPC CR the instruction

should affect (only applies to UDI op-codes that can set

CR bits, see table Table 4-2, page 186).