12 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Preface: About This Guide

R

General Conventions

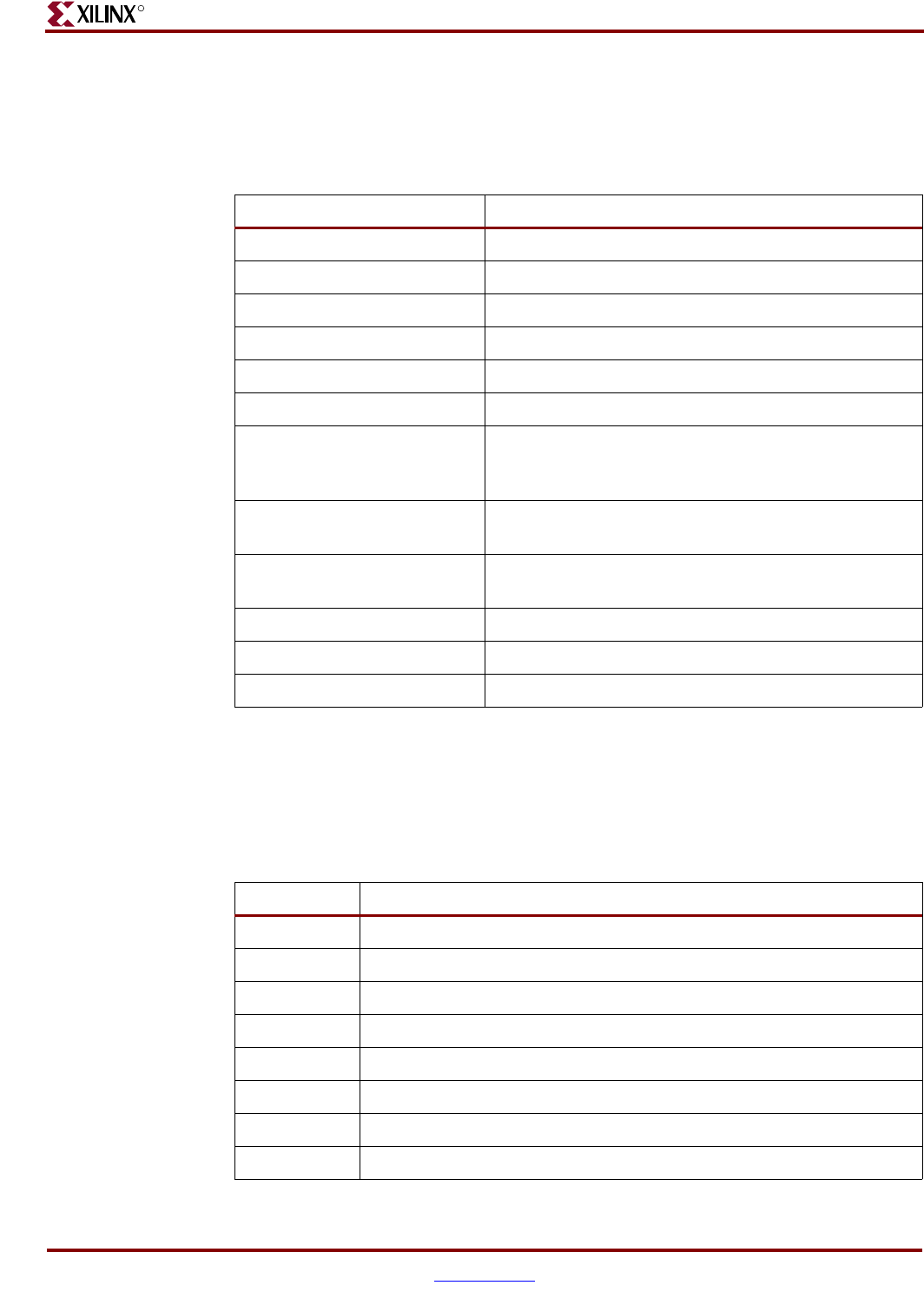

Table 1-1 lists the general notational conventions used throughout this document.

Registers

Table 1-2 lists the PowerPC 405 registers used in this document and their descriptive

names.

Table 1-1: General Notational Conventions

Convention Definition

mnemonic Instruction mnemonics are shown in lower-case bold.

variable Variable items are shown in italic.

ActiveLow An overbar indicates an active-low signal.

n A decimal number

0xn A hexadecimal number

0bn A binary number

OBJECT

b

A single bit in any object (a register, an instruction, an

address, or a field) is shown as a subscripted number or

name

OBJECT

b:b

A range of bits in any object (a register, an instruction,

an address, or a field)

OBJECT

b,b, . . .

A list of bits in any object (a register, an instruction, an

address, or a field)

REGISTER[FIELD] Fields within any register are shown in square brackets

REGISTER[FIELD, FIELD

. . .

]A

list of fields in any register

REGISTER[FIELD:FIELD] A

range of fields in any register

Table 1-2: PowerPC 405 Registers

Register Descriptive Name

CCR0 Core-configuration register 0

DBCRn Debug-control register n

DBSR Debug-status register

ESR Exception-syndrome register

MSR Machine-state register

PIT Programmable-interval timer

TBL Time-base lower

TBU Time-base upper