PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 191

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

FCM internal data hazards such as read-after-write (RAW) and write-after-write (WAW)

are eliminated if the designer ensures that all FCM instructions complete in order. This can

be done conservatively by asserting FCMAPUDONE only after each instruction has

completed. This is, however, incompatible with execution pipelining. A pipelined FCM

must handle all possible hazards internally.

APU Controller Configuration

General Configuration Register

The general configuration register defines the APU Controller’s behavior. The register is 32

bits wide. Individual bits are described in Table 4-4. For reset values, refer to Table 4-10,

page 198.

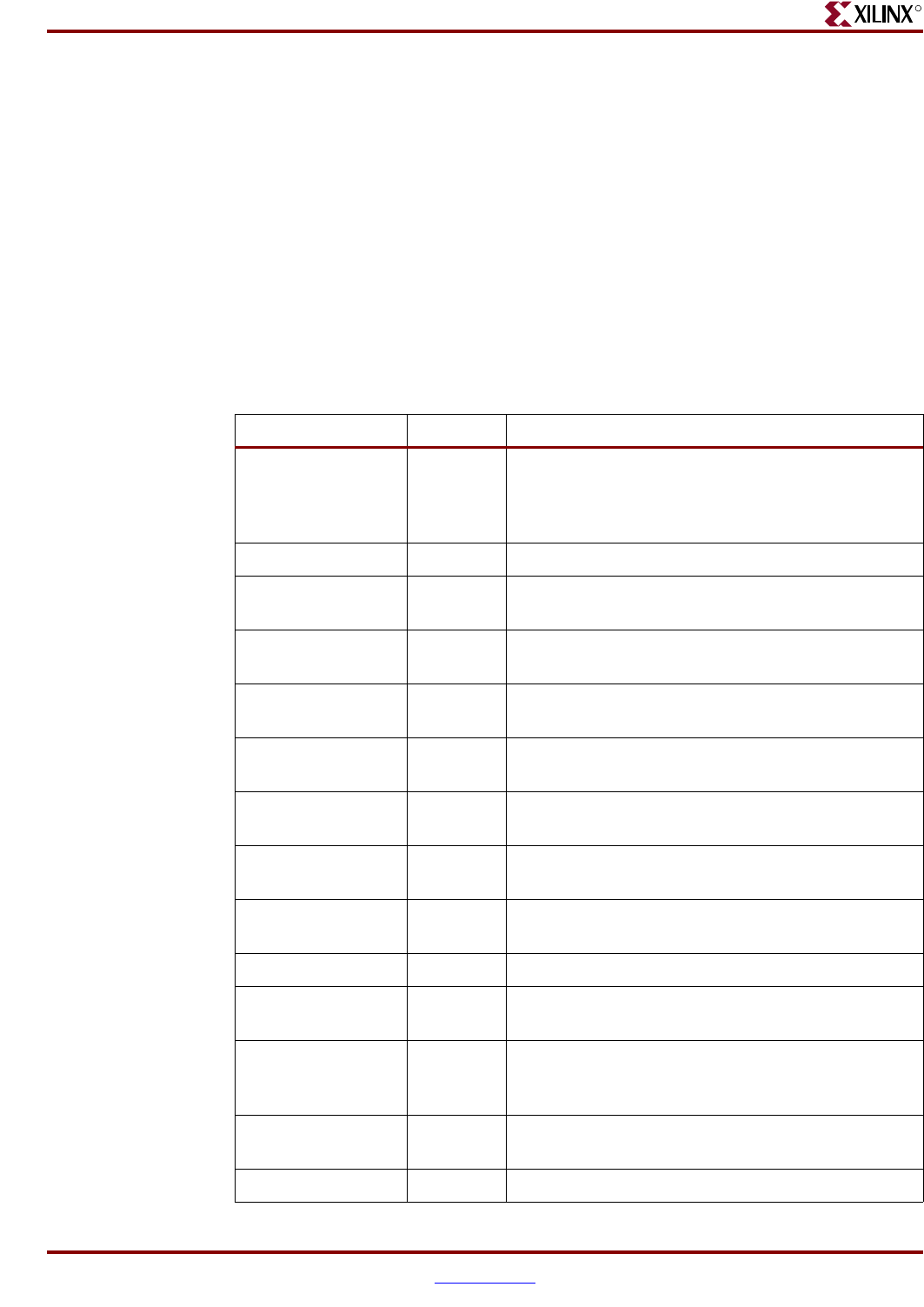

Table 4-4: APU Controller Configuration Register Bit Description

Name Bit Description

RstUDICfg 0 Reset the UDI configuration registers by loading

attribute interface signals (TIEAPUUDIn).

Reset the APU Controller Configuration register by

loading TIEAPUCONTROL.

-(1:4)Not used.

LdStDecDis 5 Disable Load/Store instruction decoding only in

APU Controller.

UDIDecDis 6 Disable UDI instruction decoding in APU Controller.

This bit also disables load store instruction decoding.

ForceUDINonB 7 Force all UDI instructions to execute as if Non-

Blocking.

FPUDecDis 8 Disable FPU instruction decoding in APU

Controller.

FPUCArithDis 9 Disable decoding of FPU complex arithmetic

instruction group (see “Floating Point Instructions”).

FPUConvIDis 10 Disable decoding of FPU conversion instruction

group (see “Floating Point Instructions”).

FPUEstimIDis 11 Disable decoding of FPU estimation instruction

group (see “Floating Point Instructions”).

- (12:14) Not used.

ForceFPUNonB 15 Force all FPU instructions to execute as if they are

non-blocking.

StoreWBOK 16 Enable generation of the APUFCMWRITEBACKOK

signal for FCM Store operations (see “FCM

Instruction Flushing”).

LdStPrivOp 17 Execute Load/Store operations only in priviliged

mode.

- (18:19) Not used.