150 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 3: PowerPC 405 OCM Controller

R

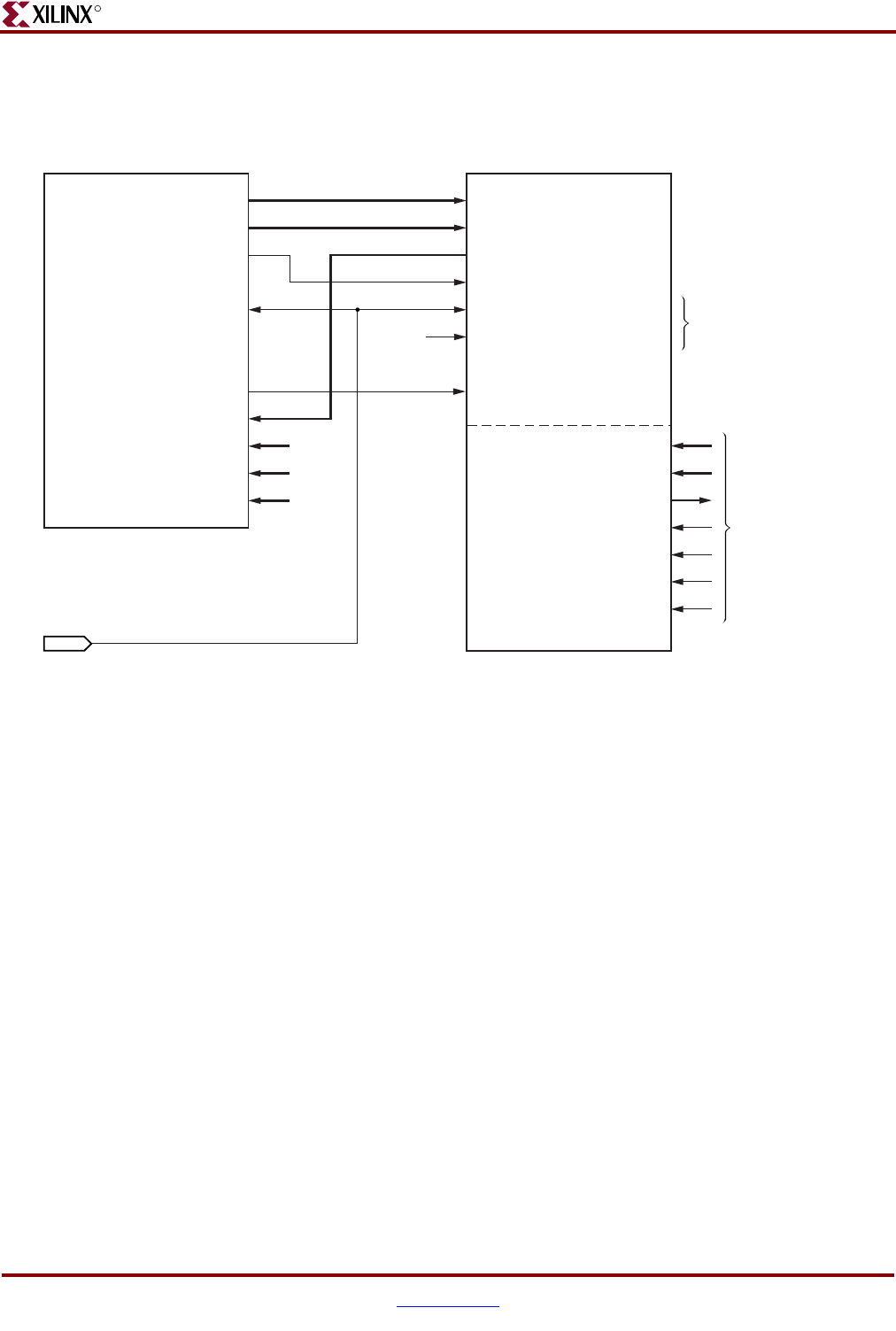

Figure 3-4: DSOCM to BRAM Interface: 8-KByte Example for Virtex-II Pro

UG018_48_112103

DSOCMBRAMABUS[19:29]

DSOCMBRAMWRDBUS[0:31]

DSOCMBRAMBYTEWRITE[0:3]

BRAMDSOCMCLK

DSOCMBRAMEN

BRAMDSOCMRDDBUS[0:31]

DSCNTLVALUE[0:7]

DSARCVALUE[0:7]

TIEDSOCMDCRADDR[0:7]

(Virtex-II Pro Only)

ADDRA[10:0]

DIA[7:0]

DOA[7:0]

WEA

CLKA

SSRA

ENA*

(RAMB16S9S9) X 4

ADDRB[13:3]

PORT A

PORT B

DIB[7:0]

DOB[7:0]

WEB

To/from FPGA logic

(application-specific use

)

CLKB

ENB

SSRB

(BRAMDSOCMCLK from DCM)

*ENA can be tied off

permanently for higher

performance.

Global signals from FPGA

system interface