226 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

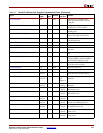

Appendix C: Processor Block Timing Model

R

Clock:

T

CPWH

Clock Pulse Width, High

State

CPMC405CLOCK

T

CPWL

Clock Pulse Width, Low State CPMC405CLOCK

a. Virtex-II Pro only. See Table C-3 for Virtex-4 DCR bus timing parameters.

Table C-2: Parameters Relative to the Core Clock (CPMC405CLOCK) (Continued)

Parameter Function Signals