18 www.xilinx.com PowerPC™ 405 Processor Block Reference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Chapter 1: Introduction to the PowerPC 405 Processor

R

The PowerPC architecture requires that all PowerPC implementations adhere to the UISA,

offering compatibility among all PowerPC application programs. However, different

versions of the VEA and OEA are permitted.

Embedded applications written for the PowerPC 405 are compatible with other PowerPC

implementations. Privileged software generally is not compatible. The migration of

privileged software from the PowerPC architecture to the PowerPC 405 is in many cases

straightforward because of the simplifications made by the PowerPC embedded-

environment architecture. Refer to the PowerPC Processor Reference Guide for more

information on programming the PowerPC 405.

PowerPC Embedded-Environment Architecture

The PowerPC 405 is an implementation of the PowerPC embedded-environment

architecture. This architecture is optimized for embedded controllers and is a forerunner to

the PowerPC Book-E architecture. The PowerPC embedded-environment architecture

provides an alternative definition for certain features specified by the PowerPC VEA and

OEA. Implementations that adhere to the PowerPC embedded-environment architecture

also adhere to the PowerPC UISA. PowerPC embedded-environment processors are 32-bit

only implementations and thus do not include the special 64-bit extensions to the PowerPC

UISA. Also, floating-point support can be provided either in hardware or software by

PowerPC embedded-environment processors.

The following are features of the PowerPC embedded-environment architecture:

x Memory management optimized for embedded software environments.

x Cache-management instructions for optimizing performance and memory control in

complex applications that are graphically and numerically intensive.

x Storage attributes for controlling memory-system behavior.

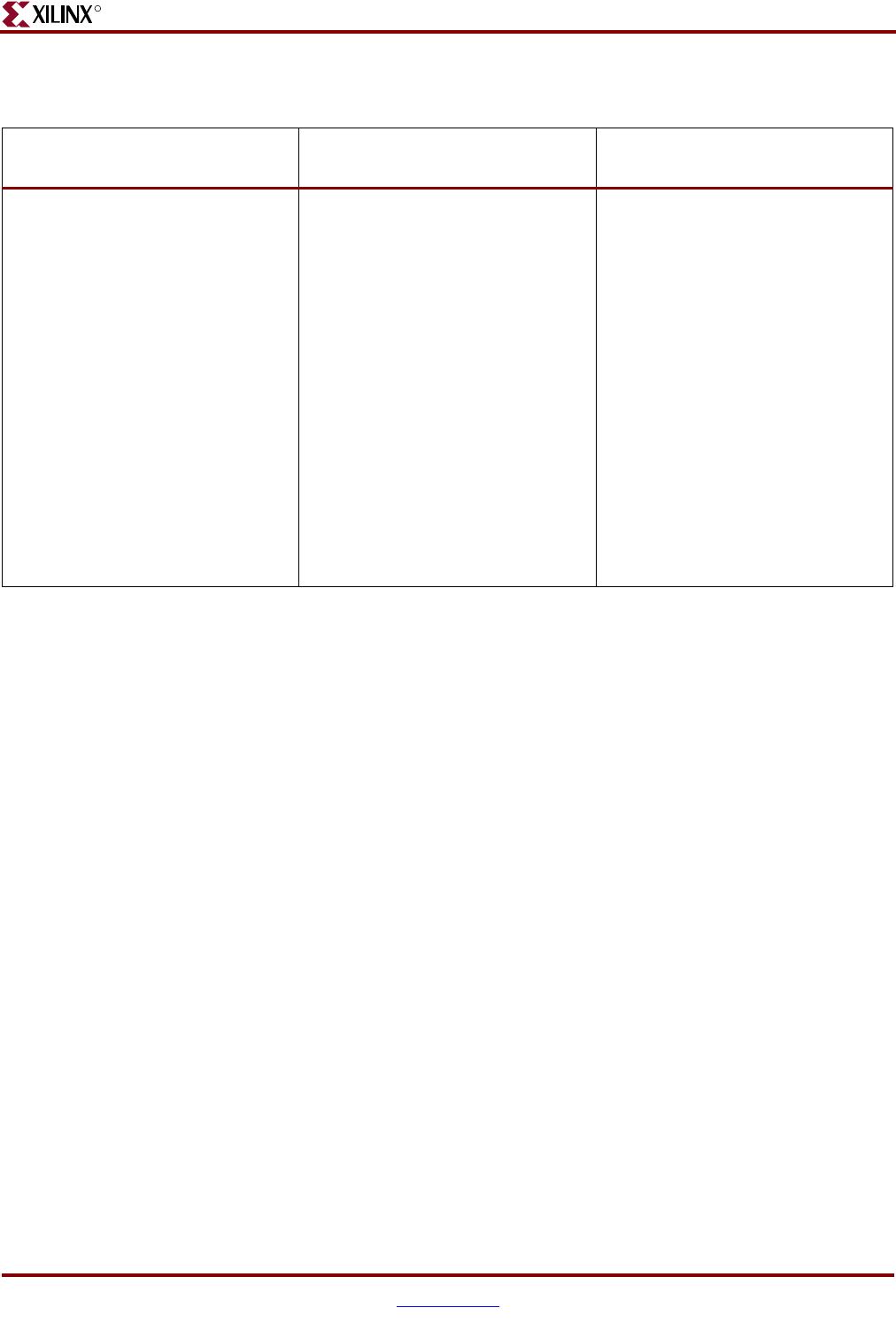

Table 1-1: Three Levels of PowerPC Architecture

User Instruction-Set Architecture

(UISA)

Virtual Environment Architecture

(VEA)

Operating Environment

Architecture (OEA)

x

Defines the architecture level to

which user-level (sometimes

referred to as problem state)

software should conform

x Defines the base user-level

instruction set, user-level

registers, data types, floating-

point memory conventions,

exception model as seen by user

programs, memory model, and

the programming model

x Defines additional user-level

functionality that falls outside

typical user-level software

requirements

x Describes the memory model for

an environment in which

multiple devices can access

memory

x Defines aspects of the cache

model and cache-control

instructions

x Defines the time-base resources

from a user-level perspective

x

x

Defines supervisor-level

resources typically required by

an operating system

x Defines the memory-

management model, supervisor-

level registers, synchronization

requirements, and the exception

model

x Defines the time-base resources

from a supervisor-level

perspective

Note: All PowerPC implementations

adhere to the UISA.

Note: Implementations that conform to

the VEA level are guaranteed to conform

to the UISA level.

Note: Implementations that conform to

the OEA level are guaranteed to conform

to the UISA and VEA levels.