PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 189

UG018 (v2.0) August 20, 2004 1-800-255-7778

R

The extended op-code for Load/Store operations are described in Table 4-3.

APU Controller Load/Store instruction decoding can be disabled in the APU Controller

configuration register.

The PowerPC405 native VMX instructions are a subset of the supported FCM Load/Store

instructions.

APU Controller User-Defined Instruction Decoding

In addition to the pre-defined instructions described previously, the user can also define

up to eight custom instructions to be decoded by the APU Controller. The instructions

conform to the same standard FCM format presented earlier, however, the interpretation of

the RA, RB, and RT fields are up to the FCM. The UDI interaction with the PowerPC405

pipeline is defined in the APU Controller UDI configuration registers. When there are user

instructions being decoded by the APU, the FCM will receive the bit-encoded UDI register

number that was decoded (along with the 32-bit instruction). For details refer to the “APU

Controller Configuration” section in this chapter.

FCM Pre-Defined Instruction Decoding

There is one group of pre-defined PowerPC instructions that can be configured to be

decoded in the FCM: integer divide instructions.

Integer Divide Instructions

The PowerPC integer divide instruction constitutes a special case. While it would normally

be executed in the PowerPC natively (consuming 35 cycles), the APU Controller can be

configured to give the FCM ownership of decoding and executing integer divide

instructions (listed below). See the section “APU Controller Configuration,” page 191, for

details on enabling the FCM divide.

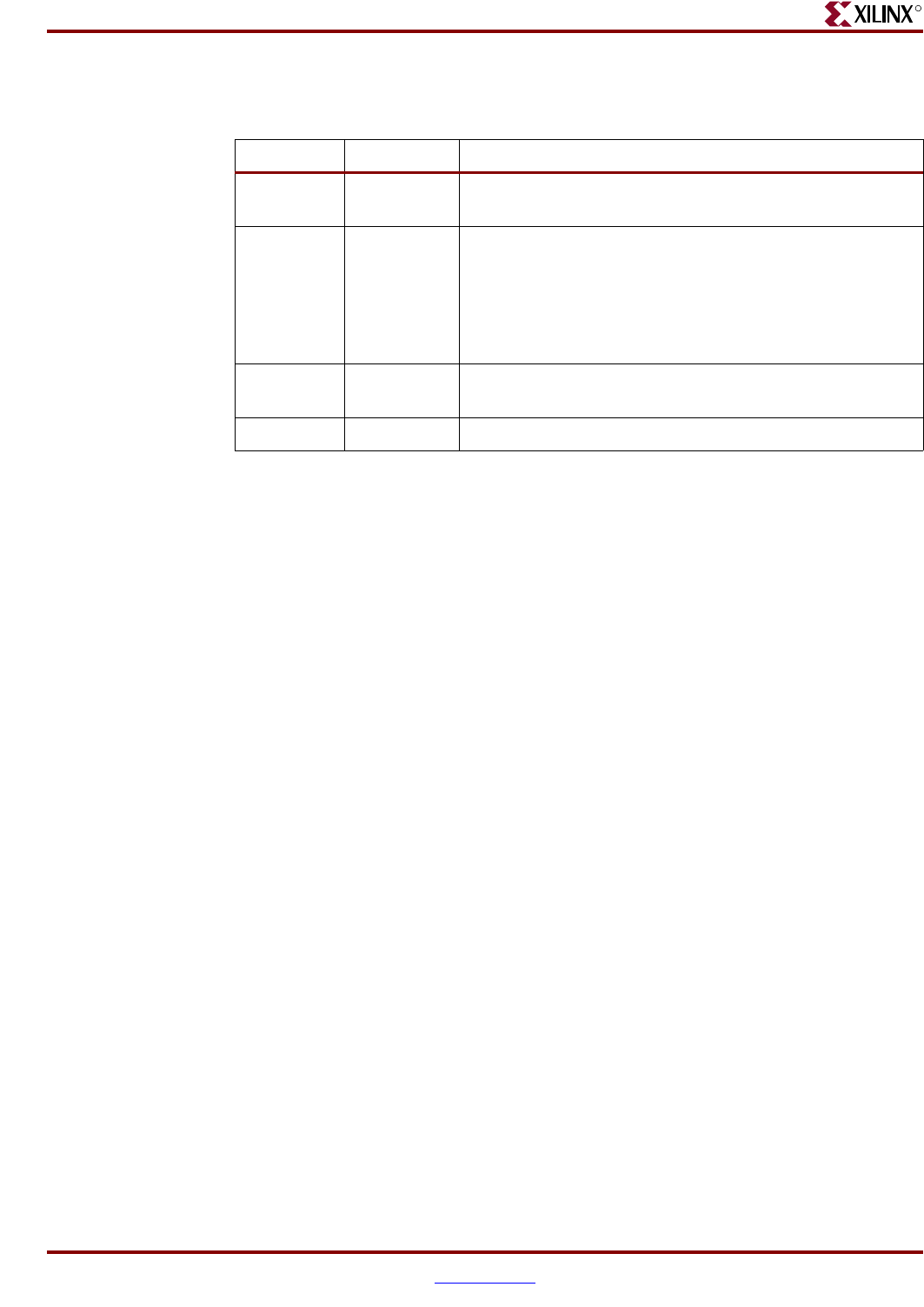

Table 4-3: Load/Store Extended Op-code

Field Bit position Description

U 21 Update: If 1 then load RA with effective address:

RA <- (RA|0)+(RB)

W[0:2] (22,24:25) 0b000 = Byte

0b001 = Half-word

0b010 = Word

0b-11 = Quad-word

0b100 = Double-word

0b101,0b110 = illegal

L/S 23 0 = Load

1 = Store

- (26:31) hard coded 0b001110

x d

ivd

x

divdo

x

divdu

x

divduo

x

divw

x

divw.

x

divwo

x

divwo.

x

divwu

x

divwu.

x

divwuo

x

divwuo.