1-18

Introduction

Status Reporting

Standard Event

Status Register

The Standard Event Status Register (SESR) monitors the following instrument status events:

• PON - Power On

• CME - Command Error

• EXE - Execution Error

• DDE - Device Dependent Error

• QYE - Query Error

• RQC - Request Control

• OPC - Operation Complete

When one of these events occurs, the corresponding bit is set in the register. If the corre-

sponding bit is also enabled in the Standard Event Status Enable Register, a summary bit

(ESB) in the Status Byte Register is set. The contents of the Standard Event Status Register

can be read and the register cleared by sending the *ESR? query. The value returned is the

total bit weights of all of the bits set at the present time. If bit 4 (weight = 16) and bit 5

(weight = 32) are set, the program prints the sum of the two weights.

This example uses the *ESR? query to read the contents of the Standard Event Status Regis-

ter.

10 OUTPUT 707;":SYSTEM:HEADER OFF"!Turn headers off

20 OUTPUT 707;"*ESR?"

30 ENTER 707;Result!Place result in a numeric variable

40 PRINT Result!Print the result

50 End

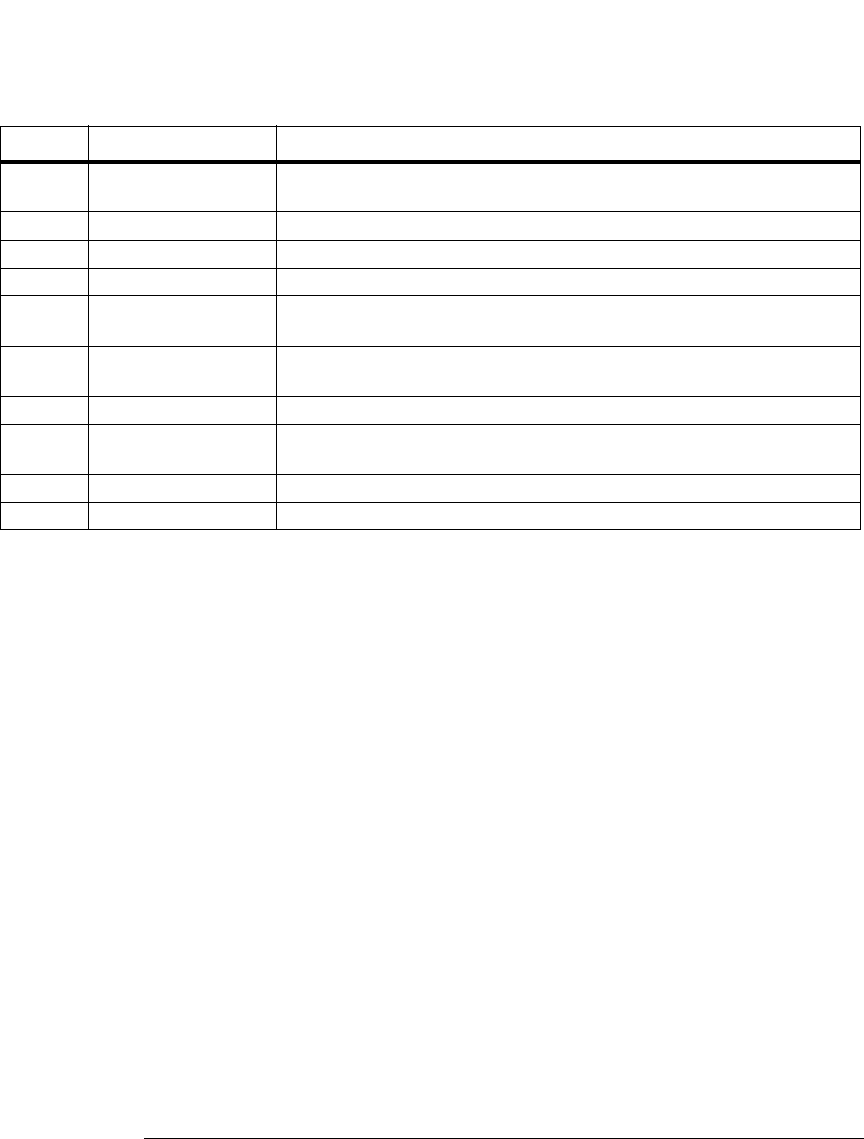

PTIME Precision Timebase Indicates that one of the enabled conditions in the Precision Timebase Register has

occurred.

QYE Query Error Indicates if the protocol for queries has been violated.

RQL Request Control Indicates if the device is requesting control.

RQS Request Service Indicates that the device is requesting service.

SPR1 Signal Present

Receiver 1

Indicates that the Clock Recovery Module has detected an optical signal on receiver

one.

SPR2 Signal Present

Receiver 2

Indicates that the Clock Recovery Module has detected an optical signal on receiver

two.

TRG Trigger Indicates if a trigger has been received.

UNLK UNLoCKed Indicates that an unlocked or trigger loss condition has occurred in the Clock Recovery

Module.

URQ Not used. Permanently set to zero.

USR User Event Register Indicates if any of the enabled conditions have occurred in the User Event Register.

Table 1-5. Status Reporting Bit Definition (2 of 2)

Bit Description Definition