4-11

Root Level Commands

OPEE

Returned Format [:MTER] <value><NL>

OPEE

Command :OPEE <mask>

This command sets a mask in the Operation Status Enable register. Each bit that is set to a

“1” enables that bit to set bit 7 in the Status Byte Register, and potentially causes an SRQ to

be generated. Bit 5, Wait for Trig, is used. Other bits are reserved. <mask> The decimal

weight of the enabled bits.

Query :OPEE?

The query returns the current value contained in the Operation Status Enable register as a

decimal number.

Returned Format [:OPEE] <value><NL>

OPER?

Query :OPER?

This query returns the value contained in the Operation Status Register as a decimal number

and also clears this register. This register is the summary of the CLCK bit (bit 7), LTEST bit

(bit 8), ACQ bit (bit 9) and MTEST bit (bit 10). The CLCK bit is set by the Clock Recovery

Event Register and indicates that a clock event has occurred. The LTEST bit is set by the

Limit Test Event Register and indicates that a limit test has failed or completed. The ACQ bit

is set by the Acquisition Event Register and indicates that an acquisition limit test has com-

pleted. The MTEST bit is set by the Mask Test Event Register and indicates that a mask limit

test has failed or completed.

Returned Format [:OPER] <value><NL>

PTEE

Command :PTEE <mask>

This command sets a mask into the Precision Timebase Event Enable register. A “1” in a bit

position enables the corresponding bit in the Precision Timebase Event Register to set bit 11

in the Operation Status Register. <mask> is the decimal weight of the enabled bits. Only bit 0

of the Precision Timebase Event Register are used at this time. The useful mask values are

shown in the following table. The following table shows the enabled bits for each useful mask

value. Bits that are not marked as enabled for a mask are blocked from affecting the opera-

tion status register.

Restrictions Software revision A.03.01 and above

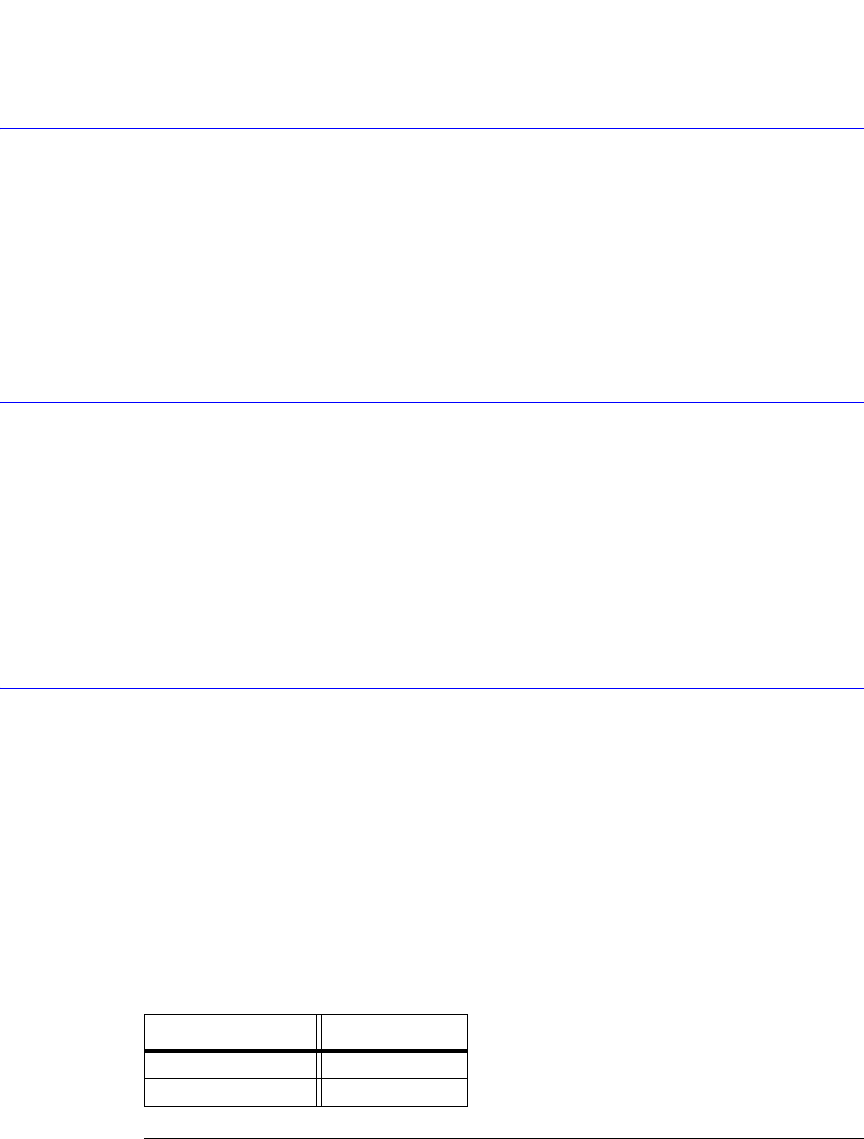

Table 4-7. Enabled Bits for Mask Values

Mask Value Bit 0 LOSS

0

1•