8-20 PXA250 and PXA210 Applications Processors Design Guide

Power and Clocking

8.7 Example Form Factor Reference Design Power

Delivery Example

8.7.1 Power System

Features of the example form factor reference design power system (example in Figure 8-5,

“Example Form Factor Reference Design Power System Design” on page 8-22) are:

• A standard-size cylindrical single-cell Li+ 3.6 V battery with a 1.8 Ahr capacity

• Battery temperature monitoring thermistor during charge cycles

• Battery voltage monitoring

• Charger supply voltage fault monitoring

• Low battery interrupt signal to the microprocessor.

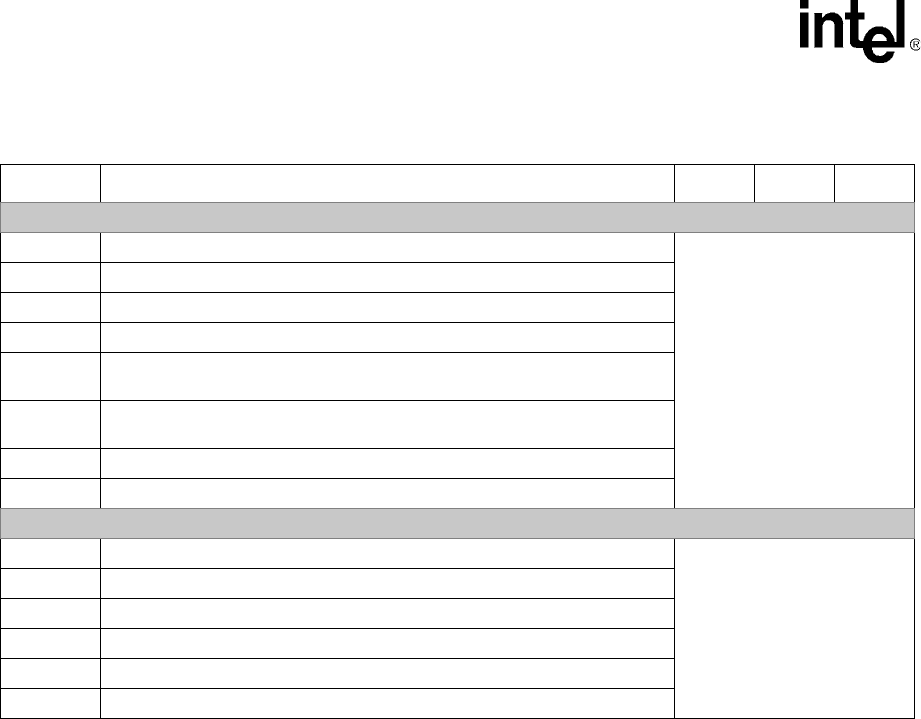

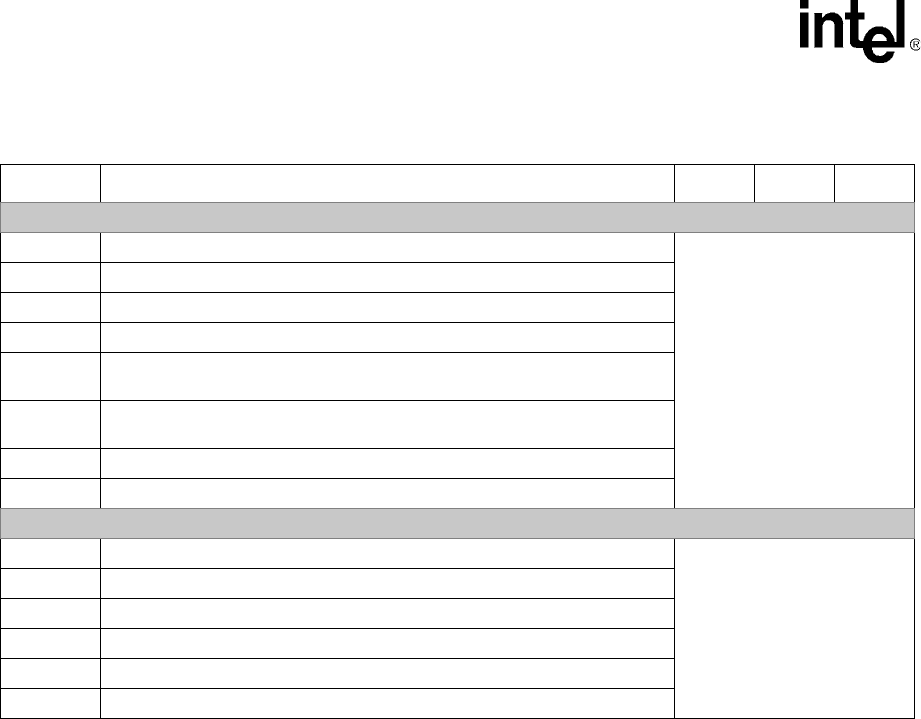

Table 8-18. Synchronous Memory Interface AC Specifications (2.5 V)

Symbol Description MIN MAX Notes

1

SDRAM / SMROM

tsynCLK SDCLK period

TBD

tsynCMD nSDCAS, nSDRAS, nWE, nSDCS assert time

tsynRCD nSDRAS to nSDCAS assert time

tsynCAS nSDCAS to nSDCAS assert time

tsynSDOS

MA(25:0), MD(31:0), DQM(3:0), nSDCS(3:0), nSDRAS, nSDCAS, nWE, nOE,

SDCKE(1:0), RDnWR output setup time to SDCLK(2:0) rise

tsynSDOH

MA(25:0), MD(31:0), DQM(3:0), nSDCS(3:0), nSDRAS, nSDCAS, nWE, nOE,

SDCKE(1:0), RDnWR output hold time from SDCLK(2:0) rise

tsynSDIS MD(31:0) read data input setup time from SDCLK(2:0) rise

tsynDIH MD(31:0) read data input hold time from SDCLK(2:0) rise

Fast Flash (Synchronous READS only)

tffCLK SDCLK period

TBD

tffAS MA(25:0) setup to nSDCAS (as nADV) asserted

tffCES nCS setup to nSDCAS (as nADV) asserted

tffADV nSDCAS (as nADV) pulse width

tffOS nSDCAS (as nADV) deassertion to nOE assertion

tffCEH nOE deassertion to nCS deassertion

NOTES:

1. These numbers are for a maximum 99.5 MHz MEMCLK and 99.5 MHz output SDCLK.

2. SDCLK for SDRAM and SMROM can be at the slowest, divide-by-2 of the 99.5 MHz MEMCLK. It can be 99.5 MHz at the

fastest.

3. This number represents 1/2 SDCLK period.

4. SDCLK for Fast Flash can be at the slowest, divide-by-2 of the 99.5 MHz MEMCLK. It can be divide-by-2 of the 132.7 MHz

MEMCLK at its fastest.