8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Pg. 4

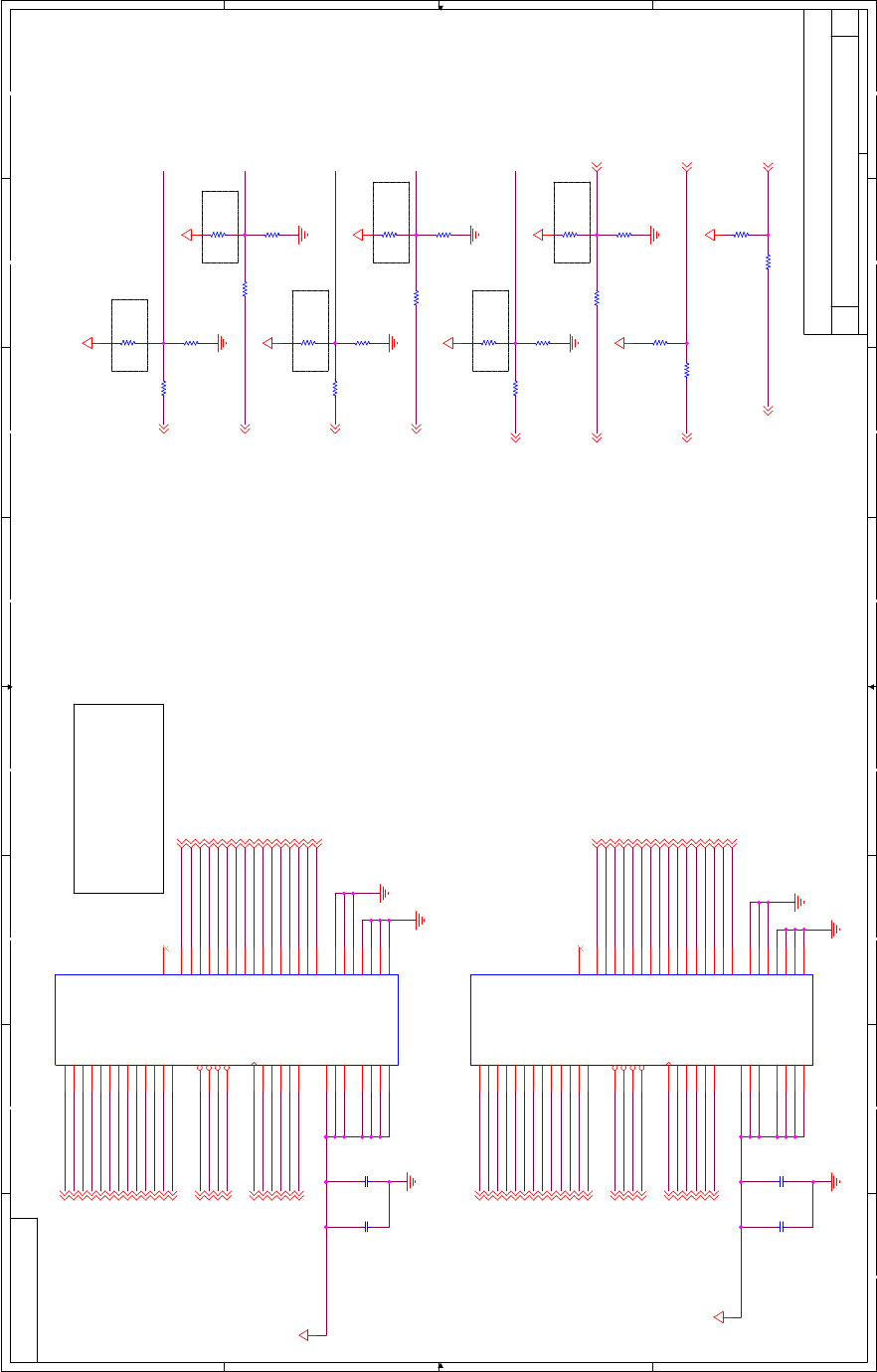

SDRAM Bank Addressing:

SDRAM Address Bus wired for

SA1110 legacy compatibility mode

for SDRAM Bank Addressing.

SDRAM

DNI

DNI

DNI

DNI

DNI

DNI

SYSTEM CONFIGURATION REGISTER

Copyright 2002 Intel Corporation

2.07

PXA250 Processor Reference Design

B

4 16Tuesday, February 05, 2002

Size Rev

Date: Sheet

of

FLASH_SZ_0

SD_SZ_0

SD_SZ_1

FLASH_SZ_1

FLASH_TYPE

SA_A19{2,5,7}

L_DD_12{3,13}

SA_A15{2,5,7}

L_DD_10{3,13}

L_DD_13{3,13}

SA_A11{2,5,7}

SA_nSDCS_0

{2,7}

L_DD_14{3,13}

SA_A20{2,5,7}

SA_A10{2,5,7}

SA_DQM_3{2,7}

SA_A20{2,5,7}

SA_nWE{2,5,6,7,10}

SA_A13{2,5,7}

SA_A17{2,5,7}

SA_A14{2,5,7}

SA_A19{2,5,7}

SA_A14{2,5,7}

nGFX_PRESENT{13,15}

SA_A23{2,5,7}

SA_A17{2,5,7}

SA_A12{2,5,7}

SA_A21{2,5,7}

SA_nSDCS_0{2,7}

SA_A22{2,5,7}

SA_nWE{2,5,6,7,10}

SA_nSDCAS

{2,5,6,7}

SA_A18{2,5,7}

SA_A24{2,5,7}

SA_A18{2,5,7}

SA_A16{2,5,7}

SA_nSDRAS{2,6,7}

SA_DQM_0{2,7}

SA_nSDCAS{2,5,6,7}

SA_A10{2,5,7}

SA_DQM_2{2,7}

SA_SDCKE_1{2,6}

SA_A16{2,5,7}

SA_A21{2,5,7}

SA_A12{2,5,7}

SA_SDCLK_1{2,7}

SA_SDCKE_1{2,6}

SA_A11{2,5,7}

SA_A15{2,5,7}

L_DD_8{3,13}

SA_A13{2,5,7}

nNEP_PRESENT{13,15}

L_DD_9{3,13}

L_DD_15{3,13}

SA_SDCLK_1{2,7}

SA_DQM_1{2,7}

SA_nSDRAS{2,6,7}

L_DD_11{3,13}

LCD_TYPE {13}

SA_A22{2,5,7}

SA_A24{2,5,7}

SA_A23{2,5,7}

SA_D14 {2,5,6,7}

SA_D15 {2,5,6,7}

SA_D26 {2,5,7}

SA_D0 {2,5,6,7}

SA_D10 {2,5,6,7}

SA_D22 {2,5,7}

SA_D12 {2,5,6,7}

SA_D19 {2,5,7}

SA_D16 {2,5,7}

SA_D1 {2,5,6,7}

SA_D20 {2,5,7}

SA_D29 {2,5,7}

SA_D25 {2,5,7}

SA_D28 {2,5,7}

SA_D6 {2,5,6,7}

SA_D30 {2,5,7}

SA_D3 {2,5,6,7}

SA_D24 {2,5,7}

SA_D11 {2,5,6,7}

SA_D31 {2,5,7}

SA_D23 {2,5,7}

SA_D8 {2,5,6,7}

SA_D5 {2,5,6,7}

SA_D9 {2,5,6,7}

SA_D2 {2,5,6,7}

SA_D13 {2,5,6,7}

SA_D27 {2,5,7}

SA_D21 {2,5,7}

SA_D18 {2,5,7}

SA_D17 {2,5,7}

SA_D4 {2,5,6,7}

SA_D7 {2,5,6,7}

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

4M x 4 x 16

SDRAM

U4

18

16

35

22

38

19

2

4

5

7

8

10

11

13

23

24

25

26

29

30

31

32

33

34

42

44

45

47

48

50

51

53

54

41

28

1

27

14

36

17

37

20

21

15

39

3

9

43

49

6

12

46

52

40

nRAS

nWE

A11

A10

CLK

nCS

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

D8

D9

D10

D11

D12

D13

D14

D15

VSS_3

VSS_2

VSS_1

VDD_1

VDD_3

VDD_2

A12

nCAS

CKE

BS_0

BS_1

LDQM

UDMQ

VDD_Q1

VDD_Q2

VDD_Q3

VDD_Q4

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

NC

C17

0.1UF

10K

R28

100K

R32

10K

R34

10K

R40

10K

R49

100K

R47

100K

R35

100K

R38

100K

R50

4M x 4 x 16

SDRAM

U5

18

16

35

22

38

19

2

4

5

7

8

10

11

13

23

24

25

26

29

30

31

32

33

34

42

44

45

47

48

50

51

53

54

41

28

1

27

14

36

17

37

20

21

15

39

3

9

43

49

6

12

46

52

40

nRAS

nWE

A11

A10

CLK

nCS

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

D8

D9

D10

D11

D12

D13

D14

D15

VSS_3

VSS_2

VSS_1

VDD_1

VDD_3

VDD_2

A12

nCAS

CKE

BS_0

BS_1

LDQM

UDMQ

VDD_Q1

VDD_Q2

VDD_Q3

VDD_Q4

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

NC

10K

R46

100K

R41

R30

0

10K

R43

R33

0

R36

0

R39

0

R42

0

R45

0

10K

R31

C20

0.1UF

100K

R29

10K

R37

C19

0.1UF

100K

R44

C18

0.1UF