8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Pg. 7

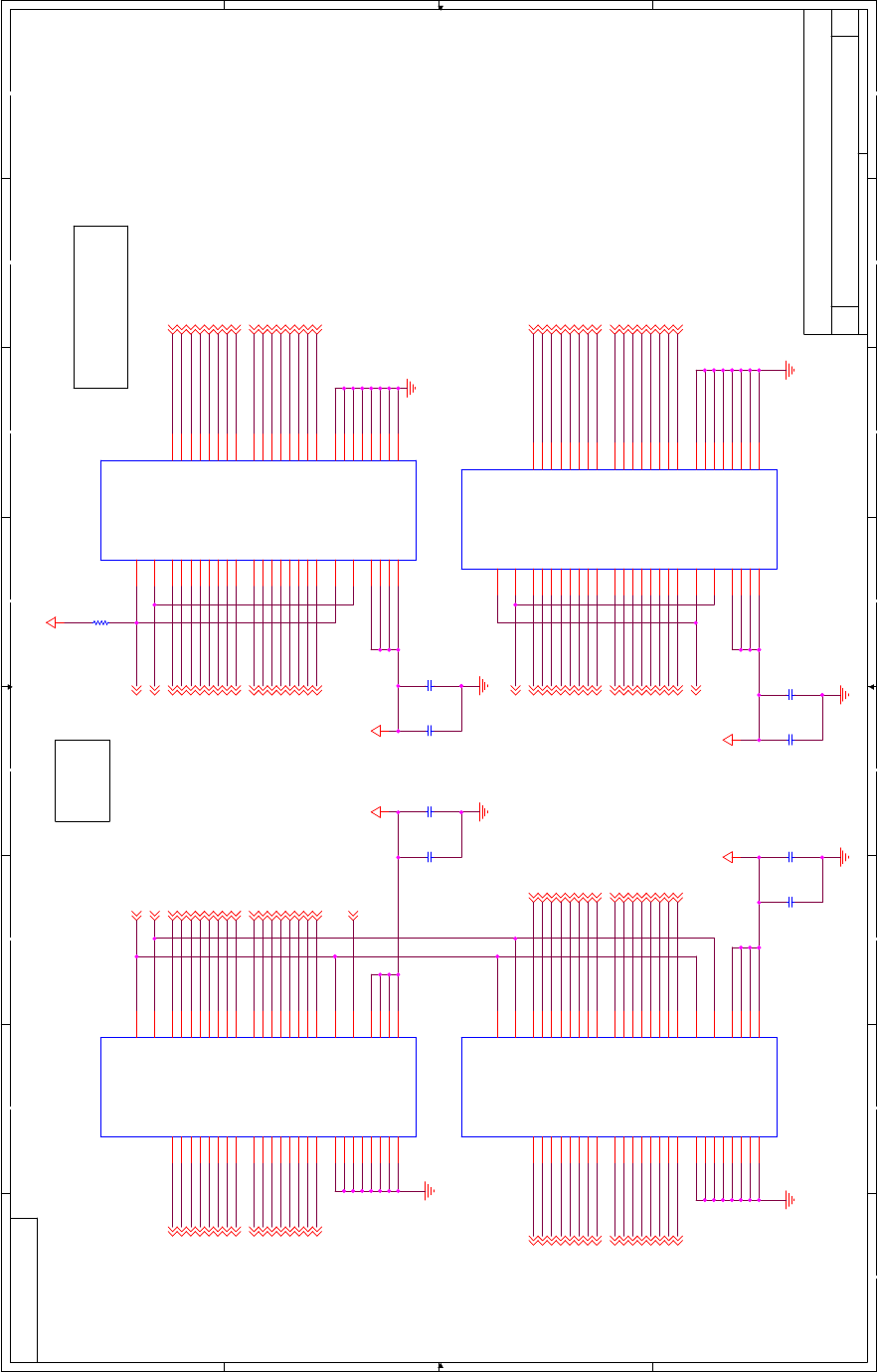

NOTE:

NOTE:

nXCV_ADD_OE is Low when

Neponset or Graphics

boards are present.

DIR H = A -> B

DIR L = A <- B

Transceivers

Copyright 2002 Intel Corporation

2.07

PXA250 Processor Reference Design

B

7 16Tuesday, February 05, 2002

Size Rev

Date: Sheet

of

VX_A21 {15}

VX_A22 {15}

SA_D1{2,4,5,6}

VX_nSDCAS{15}

SA_D18{2,4,5}

VX_DQM_1 {15}

VX_A11 {15}

nXCV_DATA_OE{6}

VX_A17 {15}

SA_D16{2,4,5}

SA_D19{2,4,5}

VX_A4 {10,15}

VX_nWE {15}

SA_D8{2,4,5,6}

VX_A18 {15}

VX_nSDCS_0{15}

SA_D20{2,4,5}

VX_A24 {15}

SA_D0{2,4,5,6}

VX_A8 {10,15}

SA_D25{2,4,5}

VX_A23 {15}

nXCV_DATA_OE{6}

VX_SDCLK_1{15}

SA_D27{2,4,5}

SA_D29{2,4,5}

VX_A19 {15}

VX_A25 {15}

SA_D12{2,4,5,6}

VX_nSDRAS{15}

nXCV_ADD_OE{6,13}

VX_A7 {10,15}

SA_D11{2,4,5,6}

VX_A13 {15}

SA_D13{2,4,5,6}

SA_D5{2,4,5,6}

VX_A16 {15}

VX_nOE {6,15}

SA_D4{2,4,5,6}

VX_DQM_2 {15}

SA_D17{2,4,5}

SA_D21{2,4,5}

VX_A12 {15}

XCV_DATA_DIR{6}

SA_D6{2,4,5,6}

SA_D7{2,4,5,6}

SA_D23{2,4,5}

SA_D31{2,4,5}

SA_D24{2,4,5}

SA_D14{2,4,5,6}

VX_A20 {15}

VX_A14 {15}

SA_D10{2,4,5,6}

VX_A15 {15}

SA_D28{2,4,5}

SA_D30{2,4,5}

VX_A10 {10,15}

SA_D2{2,4,5,6}

XCV_DATA_DIR{6}

SA_D26{2,4,5}

VX_DQM_3 {15}

SA_D15{2,4,5,6}

SA_D3{2,4,5,6}

VX_A6 {10,15}

VX_A9 {10,15}

SA_D9{2,4,5,6}

VX_DQM_0 {15}

XCV_ADD_DIR{6}

VX_A5 {10,15}

SA_D22{2,4,5}

SA_A24{2,4,5}

SA_A22{2,4,5}

SA_A23{2,4,5}

SA_A19{2,4,5}

SA_A18{2,4,5}

SA_A25{2,6}

SA_A21{2,4,5}

SA_A20{2,4,5}

SA_A13{2,4,5}

SA_A11{2,4,5}

SA_A16{2,4,5}

SA_A14{2,4,5}

SA_A17{2,4,5}

SA_A15{2,4,5}

SA_A12{2,4,5}

SA_nOE{2,5}

SA_A6{2,5}

SA_A9{2,5}

SA_A7{2,5}

SA_A8{2,5}

SA_A10{2,4,5}

SA_A5{2,5}

SA_A4{2,5}

SA_SDCLK_1{2,4}

SA_nWE{2,4,5,6,10}

SA_DQM_0

{2,4}

SA_DQM_1{2,4}

SA_DQM_2{2,4}

SA_nSDRAS{2,4,6}

SA_DQM_3{2,4}

SA_nSDCAS{2,4,5,6}

SA_nSDCS_0{2,4}

nVX_CF_OE{6}

VX_D23 {15}

VX_D9 {10,15}

VX_D16 {15}

VX_D14 {10,15}

VX_D0 {10,15}

VX_D25 {15}

VX_D26 {15}

VX_D2 {10,15}

VX_D10 {10,15}

VX_D3 {10,15}

VX_D19 {15}

VX_D12 {10,15}

VX_D30 {15}

VX_D4 {10,15}

VX_D15 {10,15}

VX_D5 {10,15}

VX_D8 {10,15}

VX_D13 {10,15}

VX_D22 {15}

VX_D29 {15}

VX_D27 {15}

VX_D18 {15}

VX_D24 {15}

VX_D1 {10,15}

VX_D31 {15}

VX_D6 {10,15}

VX_D28 {15}

VX_D21 {15}

VX_D20 {15}

VX_D17 {15}

VX_D7 {10,15}

VX_D11 {10,15}

DC3P3V

DC3P3V DC3P3V

DC3P3V

DC3P3V

C37

0.1UF

74LVCH16245A

XCVR

U12

74LVCH16245APF

1

2

3

5

6

8

9

11

12

24

25

48

47

46

44

43

41

40

38

37

26

27

29

30

32

33

35

36 13

14

16

17

19

20

22

23

7

18

31

42

4

10

15

21

28

34

39

45

1DIR

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2DIR

2nOE

1nOE

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

2A8

2A7

2A6

2A5

2A4

2A3

2A2

2A1 2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

VDD_1

VDD_2

VDD_3

VDD_4

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

C34

0.1UF

74LVCH16245A

XCVR

U13

74LVCH16245APF

1

2

3

5

6

8

9

11

12

24

25

48

47

46

44

43

41

40

38

37

26

27

29

30

32

33

35

3613

14

16

17

19

20

22

23

7

18

31

42

4

10

15

21

28

34

39

45

1DIR

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2DIR

2nOE

1nOE

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

2A8

2A7

2A6

2A5

2A4

2A3

2A2

2A12B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

VDD_1

VDD_2

VDD_3

VDD_4

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

C38

0.1UF

C35

0.1UF

74LVCH16245A

XCVR

U11

74LVCH16245APF

1

2

3

5

6

8

9

11

12

24

25

48

47

46

44

43

41

40

38

37

26

27

29

30

32

33

35

3613

14

16

17

19

20

22

23

7

18

31

42

4

10

15

21

28

34

39

45

1DIR

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2DIR

2nOE

1nOE

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

2A8

2A7

2A6

2A5

2A4

2A3

2A2

2A12B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

VDD_1

VDD_2

VDD_3

VDD_4

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

100K

R230

C39

0.1UF

C40

0.1UF

C36

0.1UF

74LVCH16245A

XCVR

U14

74LVCH16245APF

1

2

3

5

6

8

9

11

12

24

25

48

47

46

44

43

41

40

38

37

26

27

29

30

32

33

35

36 13

14

16

17

19

20

22

23

7

18

31

42

4

10

15

21

28

34

39

45

1DIR

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2DIR

2nOE

1nOE

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

2A8

2A7

2A6

2A5

2A4

2A3

2A2

2A1 2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

VDD_1

VDD_2

VDD_3

VDD_4

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

C33

0.1UF