8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

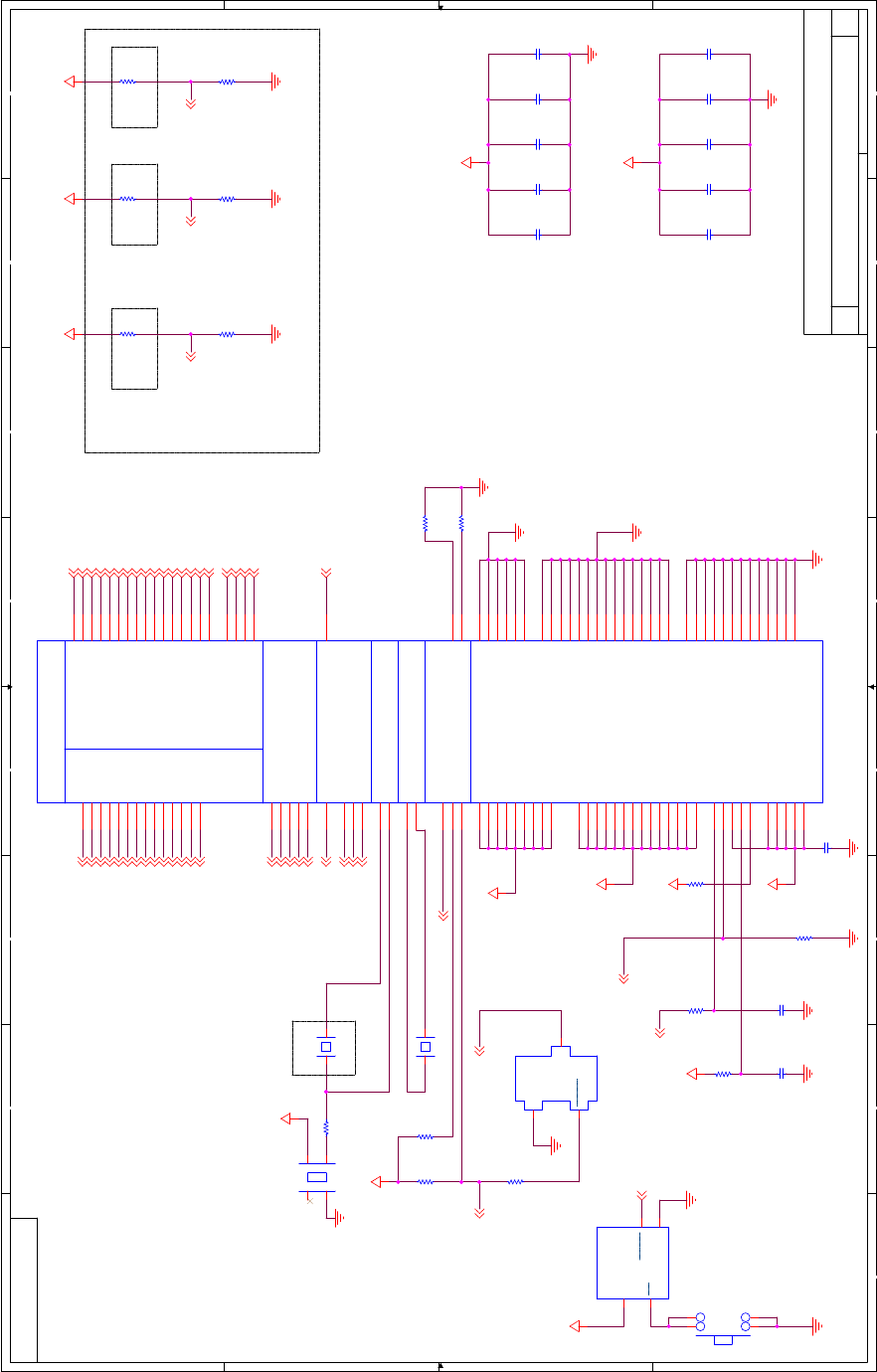

Capacitors for VDDX

Capacitors for Core

LAYOUT: Keep Close in

a Matrix and in an

Accessible location.

Add Silk screen Box.

Pg.3

DNI DNI DNI

RESET

Copyright 2002 Intel Corporation

DNI

2.07

PXA250 Processor Reference Design

B

3 16Tuesday, February 05, 2002

Size Rev

Date: Sheet

of

BOOT_SEL_0{15} BOOT_SEL_2BOOT_SEL_1{15}

CPLD2_TDO{13}

L_DD_9 {4,13}

L_DD_7 {13}

L_DD_6 {13}

L_DD_2 {13}

L_DD_14 {4,13}

BOOT_SEL_2

L_DD_1 {13}

L_BIAS {13}

L_DD_12 {4,13}

BOOT_SEL_1{15}

SA_PWR_EN{12,13}

SA_TDO{10,11}

L_DD_15 {4,13}

GPIO_0{10,15}

DC_PLL{12}

L_DD_13 {4,13}

L_DD_5 {13}

RS232_VALID{10}

L_LCLK {13}

VBATT{8,10,11,12,13,14}

AC97_IRQ{8}

MBREQ_CF_DETECT{13,15}

JTAG_nTRST{11}

L_DD_4 {13}

GPIO_17{10}

nVBATT_LOW_IRQ{12,15}

L_DD_3 {13}

JTAG_TMS{6,10,11,13}

nRESET_IN{10,11,15}

GFX_IRQ_CF_BVD2{10,15}

MBGNT_CF_IRQ{6,15}

nRESET_OUT{6,11,13,15}

nVDD_FAULT{13}

JTAG_TCK{6,10,11,13}

L_PCLK {13}

BOOT_SEL_0{15}

L_DD_11 {4,13}

L_FCLK {13}

SA1111_IRQ_CF_BVD1{10,15}

L_DD_0 {13}

L_DD_10 {4,13}

nCHRGR_PRESENT{2,12}

L_DD_8 {4,13}

PLL_SENSE{12}

SA_I2C_ENAB{10}

GPIO_11{13}

USB_WAKE

{9,15}

GPIO_32{10}

nRESET_IN{10,11,15}

DC_CORE

DC3P3V DC3P3VDC3P3V

DC3P3V

DC3P3V

DC3P3V

DC_CORE

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

C123

0.1UF

R200

0

R48

0

C15

0.1UF

C16

0.1UF

R51

0

R277

0

LCD Port

GPIO Port

JTAG

3.6Mhz

32Khz

Intel PXA250 Processor

BALL 12-11-00

U1B

PXA250_MBGA256

C16

H8

H9

J8

J9

T1

K7

K9

J10

C2

E2

G2

J2

L2

N2

R2

R4

R6

R8

R10

R12

R14

M15

P15

F6

G8

G10

H7

C4

C14

C11

J14

C8

C6

A1

D4

F4

H4

K4

M4

M14

N5

N7

N9

N11

N13

P3

T16

G14

J15

J16

T2

D15

M11

F11

G7

G9

H10

J7

K8

K10

L6

L9

L14

C10

C13

E7

D7

C7

B7

E6

D6

E5

A6

C5

A5

D5

A4

A3

A2

C3

B3

E8

D8

B8

A8

L10

L12

L13

K14

J12

J11

A16

G15

F12

F7

A7

B4

B5

H12

H15

H16

H13

H11

G11

G12

J13 K11

G16

G13

F13

K15

K16

L16

L15

L11

K12

K13

E14

D12

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSSQ_11

VSSQ_12

VSSQ_9

VSSN_1

VSSN_2

VSSN_3

VSSN_4

VSSN_5

VSSN_6

VSSN_7

VSSN_8

VSSN_9

VSSN_10

VSSN_11

VSSN_12

VSSN_13

VSSN_14

VSSN_15

VSSQ_5

VSSQ_6

VSSQ_7

VSSQ_8

VSSQ_1

VSSQ_4

VSSQ_3

VSSQ_10

VSSQ_2

VDDQ_1

VDDN_1

VDDN_2

VDDN_3

VDDN_4

VDDN_5

VDDN_6

VDDN_7

VDDN_8

VDDN_9

VDDN_10

VDDN_11

VDDN_12

VDDN_13

VDDN_14

VDDQ_5

PLL_VCC

PLL_SENSE

VCCKP

ADC_VCC

BATT_VCC

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VSSQ_13

VDDQ_2

VDDQ_3

L_DD_0_GPIO58

L_DD_1_GPIO59

L_DD_2_GPIO60

L_DD_3_GPIO61

L_DD_4_GPIO62

L_DD_5_GPIO63

L_DD_6_GPIO64

L_DD_7_GPIO65

L_DD_8_GPIO66

L_DD_9_GPIO67

L_DD_10_GPIO68

L_DD_11_GPIO69

L_DD_12_GPIO70

L_DD_13_GPIO71

L_DD_14_GPIO72

L_DD_15_GPIO73

L_FCLK_GPIO74

L_LCLK_GPIO75

L_PCLK_GPIO76

L_BIAS_GPIO77

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_32

GPIO_7

GPIO_9

GPIO_10

GPIO_11

GPIO_14

GPIO_13

TCK

TDI

TDO

TMS

nTRST

TESTCLK

TEST

nRESET nRESET_OUT

BOOT_SEL_0

BOOT_SEL_1

BOOT_SEL_2

PXTAL

PEXTAL

TXTAL

TEXTAL

PWR_EN

nBATT_FAULT

nVDD_FAULT

VDDQ_4

GPIO_17

100K

R21

100K

R22

C13

0.1UF

C8

0.1UF

10K

R23

C10

0.1UF

R262

0

32.768KHZ

Y2

2 1

10K

R25

3.6864Mhz

Y4

1

2 3

4

100K

R18

C14

0.1UF

100K

R19

100K

R20

C7

0.1UF

C11

0.1UF

C125

0.1UF

MAX6328

U2

MAX6328XR27-T-SC

2

3

1

RESET

VIN

GND

Top

B

7A

S1

1 2

34

C9

0.1UF

MAX811TEUS-T

U3

3

4

2

1

MR

VCC

RESET

GND

R271

681

C12

0.1UF

3.6864MHZ

Y1

12

1_Ohm

R26

1_Ohm

R27

10K

R24

C6

0.1UF