8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

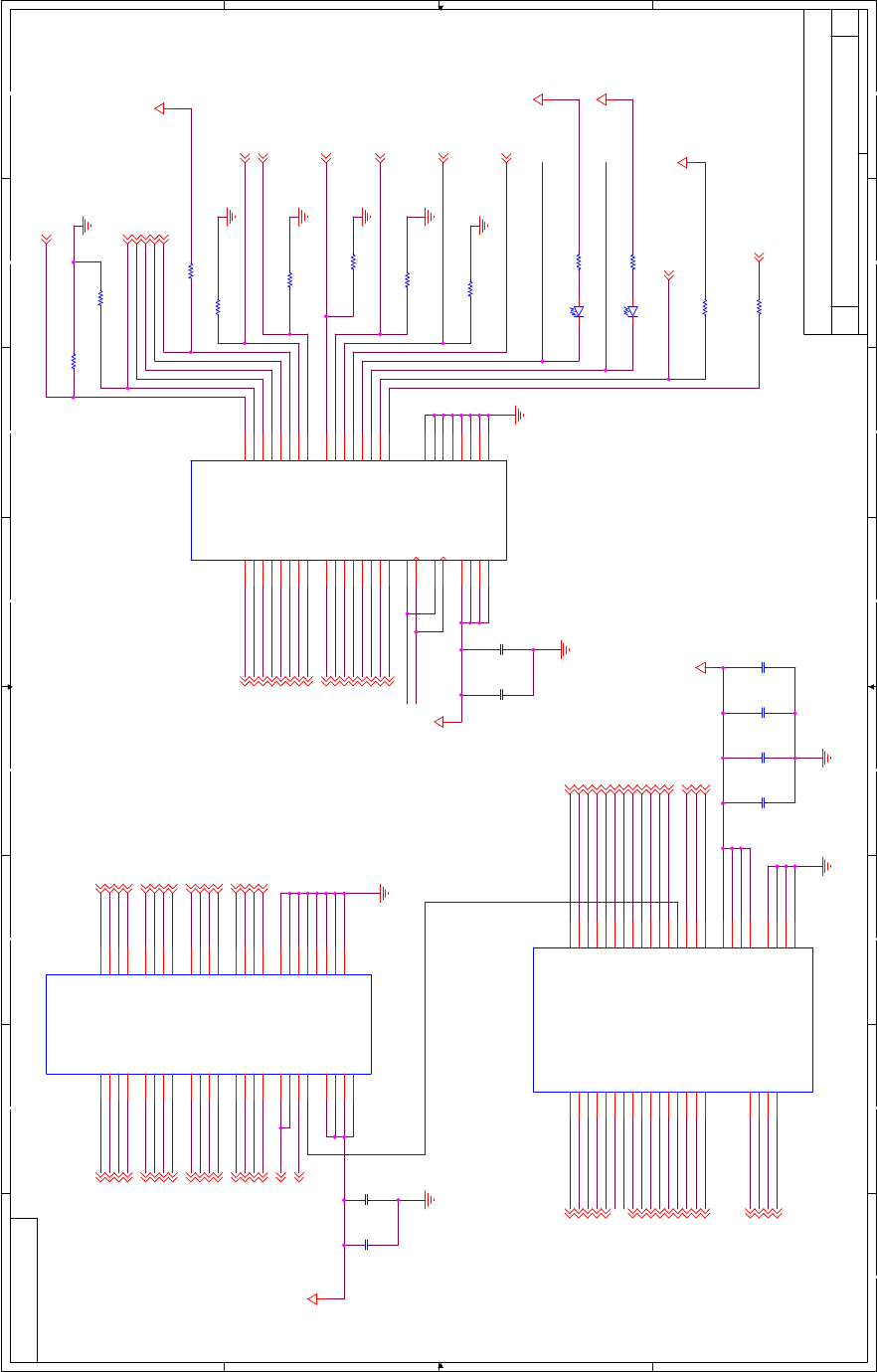

Pg. 6

Buffer

CPLD

Board Control

Register

Copyright 2002 Intel Corporation

2.07

PXA250 Processor Reference Design

B

6 16Tuesday, February 05, 2002

Size Rev

Date: Sheet

of

nRED_LED

nBCR_WR

nGREEN_LED

nBCR_WR

nBCR_OE

nBCR_OE

VX_nOE {7,15}

SA_D15{2,4,5,7}

JTAG_TMS{3,10,11,13}

SA_nSDCS_2{2}

SA_A3{2,5}

SA_A1{2}

SA_D0{2,4,5,7}

nFLASH_BOOT_CS{5}

CF_nPWAIT

{10}

CF_nPCE_1 {10}

CF_nBUS_ON

CF_nBUS_ON

SA_nPCE_1

{2,15}

SA_nPIOW{2,15}

IRDA_MD0 {9}

SA_D10{2,4,5,7}

IRDA_FSEL {9}

nXCV_ADD_OE {7,13}

SA_nIOIS16 {2,15}

nNEP_REG_CS{10,15}

VX_SDCKE_1 {15}

SA_D5{2,4,5,7}

SA_nSDCS_2

{2}

SA_nCS_4 {2,15}

nXCV_DATA_OE

{7}

SA_D13{2,4,5,7}

RS232_ON {10}

MBGNT_CF_IRQ{3,15}

SA_nPIOR

{2,15}

nVX_CF_OE{7}

SA_D9{2,4,5,7}

SA_nCS_1 {2}

SA_D14{2,4,5,7}

SPKR_OFF {8}

SA_A0

{2}

SA_RD_nWR{2,15}

SA_nPCE_1 {2,15}

SA_D6{2,4,5,7}

CF_nBUS_ON

CF_nPIOW {10}

nNEP_FLASH_CS{15}

SWAP_FLASH{15}

VX_A3 {10,15}

VX_A0 {10,15}

JTAG_TCK {3,10,11,13}

CF_nPOE {10}

SA_nPCE_2 {2,15}

SA_D3{2,4,5,7}

SA_D1{2,4,5,7}

CF_PWR_ON {13}

SA_nPREG{2,15}

IRDA_MD1 {9}

SA_SDCKE_1{2,4}

CF_nPWE {10}

SA_D7{2,4,5,7}

VX_nSDCS_2

{15}

CF_nPIOR {10}

nVX_CF_OE{7}

CF_IRQ_LVL2OE{10,15}

SA_nPWE

{2,15}

CF_nPCE_2 {10}

SA_nPWAIT {2,15}

XCV_DATA_DIR

{7}

VX_A1 {10,15}

SA_nCS_2 {2}

SA_nSDRAS{2,4,7}

SA_D2{2,4,5,7}

CF_nPREG {10}

SA_nCS_3 {2,15}

VX_SDCLK_2

{15}

SA_A25 {2,7}

RADIO_PWR_ON {11}

SA_nSDCAS{2,4,5,7}

AUDIO_PWR_ON {8}

MMC_PWR_ON{13}

SA_D8{2,4,5,7}

SA_A2{2,5}

CF_GFX_RESET {10,15}

LIGHT_PWR_ON

{13}

VX_A2 {10,15}

SA_nCS_5 {2,15}

SA_nWE{2,4,5,7,10}

SA_D4{2,4,5,7}

CPLD1_TDO {11,13}

SA_D11{2,4,5,7}

SA_SDCLK_2{2}

SA_SDCLK_2

{2}

SA_nCS_0 {2,15}

LCD_PWR_ON {13,14}

SA_nPCE_2{2,15}

XCV_ADD_DIR{7}

CF_nIOIS16{10}

SA_nPOE{2,15}

SA_D12{2,4,5,7}

RADIO_WAKE {11}

CPLD1_TDI{10,11}

nRESET_OUT{3,11,13,15}

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

C27

0.1UF

100K

R61

100K

R64

C28

0.1UF

74LVCH16374A

16-Bit Edge Triggered

D-Type Flip Flop

U9

74LVCH16374A

25

24

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

48

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1

7

18

31

42 45

39

34

28

21

15

10

4

2CLK

2nOE

1Q1

1Q2

1Q3

1Q4

1Q5

1Q6

1Q7

1Q8

2Q1

2Q2

2Q3

2Q4

2Q5

2Q6

2Q7

2Q8

1CLK

1D1

1D2

1D3

1D4

1D5

1D6

1D7

1D8

2D1

2D2

2D3

2D4

2D5

2D6

2D7

2D8

1nOE

VDD_1

VDD_2

VDD_3

VDD_4 VSS_8

VSS_7

VSS_6

VSS_5

VSS_4

VSS_3

VSS_2

VSS_1

100K

R65

R67

1.5K

C29

0.1UF

R70

0

100K

R59

C30

0.1UF

C31

0.1UF

100K

R66

R68

1.5K

16_Bit Buffer/Line

Driver

74LVCH162244A

U8

74LVCH162244APF

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

43

44

46

47

37

38

40

41

32

33

35

36

26

27

29

30

1

24

25

48

7

18

31

42

4

10

15

21

28

34

39

45

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

3Y1

3Y2

3Y3

3Y4

4Y1

4Y2

4Y3

4Y4

1A4

1A3

1A2

1A1

2A4

2A3

2A2

2A1

3A4

3A3

3A2

3A1

4A4

4A3

4A2

4A1

1nOE

4nOE

3nOE

2nOE

VDD_1

VDD_2

VDD_3

VDD_4

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

C32

0.1UF

100K

R62

100K

R69

D2

GRN

2 1

C25

0.1UF

100K

R60

C26

0.1UF

100K

R63

RED

D1

2 1

XCR3032XL-10VQ44C

Xilinx CPLD

U10

XCR3032XL

41

42

43

44

1

2

3

5

6

29

7

8

10

11

12

13

14

15

35

34

33

32

31

30

28

27

26

25

23

22

21

20

19

18

36

24

16

4

37

39

38

40

9

17

VDD_4

A0_CLK

A1

A2

A3_TDI

A4

A5

A6

A7

VDD_3

A8_TMS

A9

A10

A11

A12

A13

A14

A15

B0

B1

B2

B3_TDO

B4

B5

B6

B7

B8_TCK

B9

B10

B11

B12

B13

B14

B15

VSS_4

VSS_3

VSS_2

VSS_1

IN0

IN1

IN2

IN3

VDD_1

VDD_2