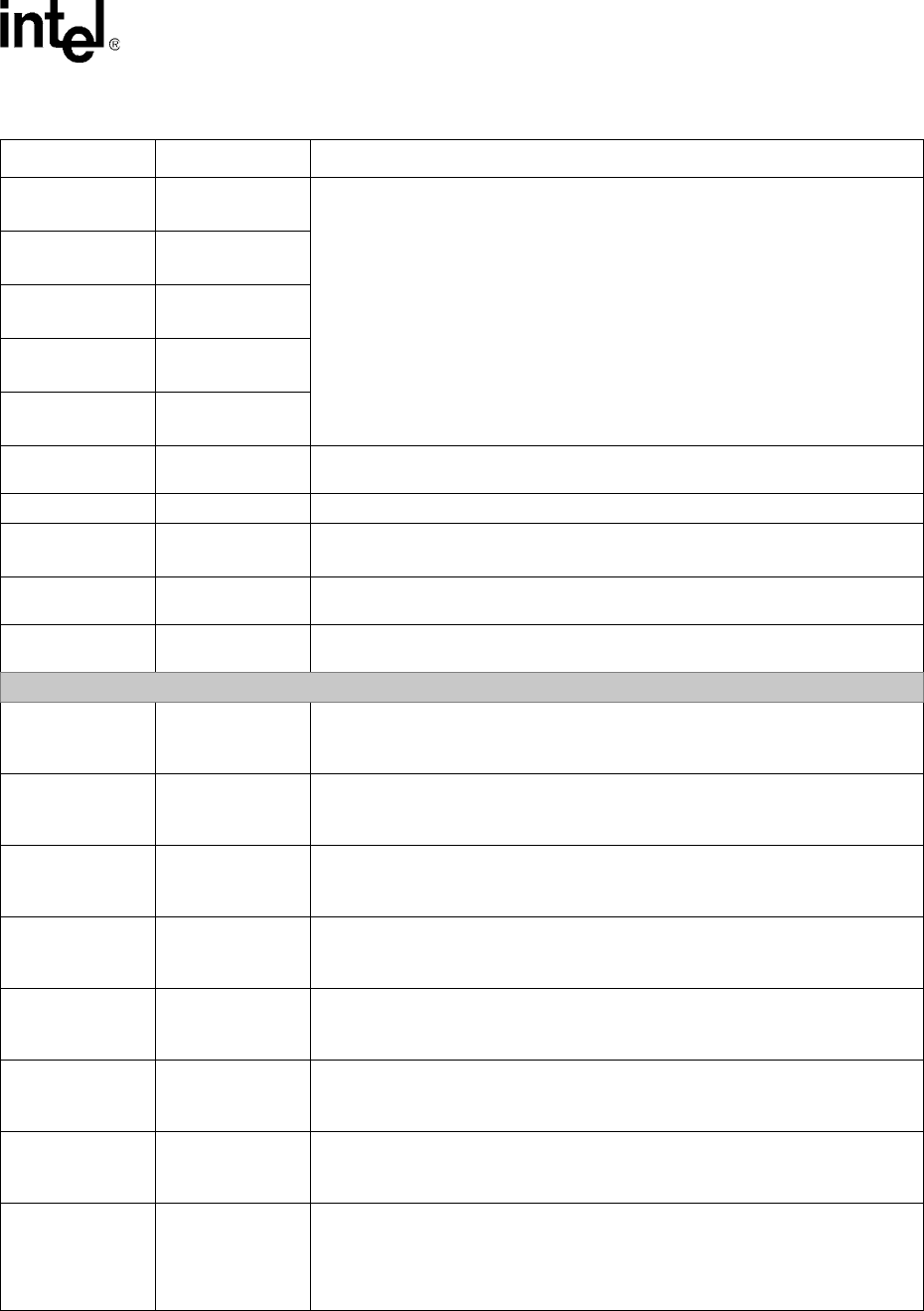

PXA250 and PXA210 Applications Processors Design Guide 1-5

Introduction

nCS[5]/

GPIO[33]

ICOCZ

Static chip selects. These signals are chip selects to static memory devices such as

ROM and Flash. They are individually programmable in the memory configuration

registers. nCS[5:3] may be used with variable data latency variable latency I/O

devices.

See Note [2]

nCS[4]/

GPIO[80]

ICOCZ

nCS[3]/

GPIO[79]

ICOCZ

nCS[2]/

GPIO[78]

ICOCZ

nCS[1]/

GPIO[15]

ICOCZ

nCS[0] ICOCZ

Static chip select 0. This is the chip select for the boot memory. nCS[0] is a dedicated

pin.

RD/nWR OCZ Read/Write for static interface. Intended for use as a steering signal for buffering logic

RDY/

GPIO[18]

ICOCZ

Variable Latency I/O Ready pin (input)

See Note [2]

MBGNT/GP[13] ICOCZ

Memory Controller grant. (output) Notifies an external device that it has been granted

the system bus.

MBREQ/GP[14] ICOCZ

Memory Controller alternate bus master request. (input) Allows an external device to

request the system bus from the Memory Controller.

PCMCIA/CF Control Pins - PXA250 Applications Processor only

nPOE/ GPIO[48] ICOCZ

PCMCIA output enable. Output PCMCIA signal that performs reads from memory and

attribute space.

See Note [2]

nPWE/

GPIO[49]

ICOCZ

PCMCIA write enable. Output signal that performs writes to memory and attribute

space.

See Note [2]

nPIOW/

GPIO[51]

ICOCZ

PCMCIA I/O write. Output signal that performs write transactions to the PCMCIA I/O

space.

See Note [2]

nPIOR/

GPIO[50]

ICOCZ

PCMCIA I/O read. Output signal that performs read transactions from the PCMCIA I/O

space.

See Note [2]

nPCE[2:1]/

GPIO[53, 52]

ICOCZ

PCMCIA card enable. Output signals that selects a PCMCIA card. Bit one enables the

high byte lane and bit zero enables the low byte lane.

See Note [2]

nIOIS16/

GPIO[57]

ICOCZ

I/O Select 16. Input signal from the PCMCIA card that indicates the current address is

a valid 16 bit wide I/O address.

See Note [2]

nPWAIT/

GPIO[56]

ICOCZ

PCMCIA wait. Input signal that is driven low by the PCMCIA card to extend the length

of the transfers to/from the applications processor.

See Note [2]

nPSKTSEL/

GPIO[54]

ICOCZ

PCMCIA socket select. Output signal used by external steering logic to route control,

address, and data signals to one of the two PCMCIA sockets. When PSKTSEL is low,

socket zero is selected. When PSKTSEL is high, socket one is selected. This signal

has the same timing as address.

See Note [2]

Table 1-3. Signal Pin Descriptions (Sheet 2 of 7)

Name Type Description