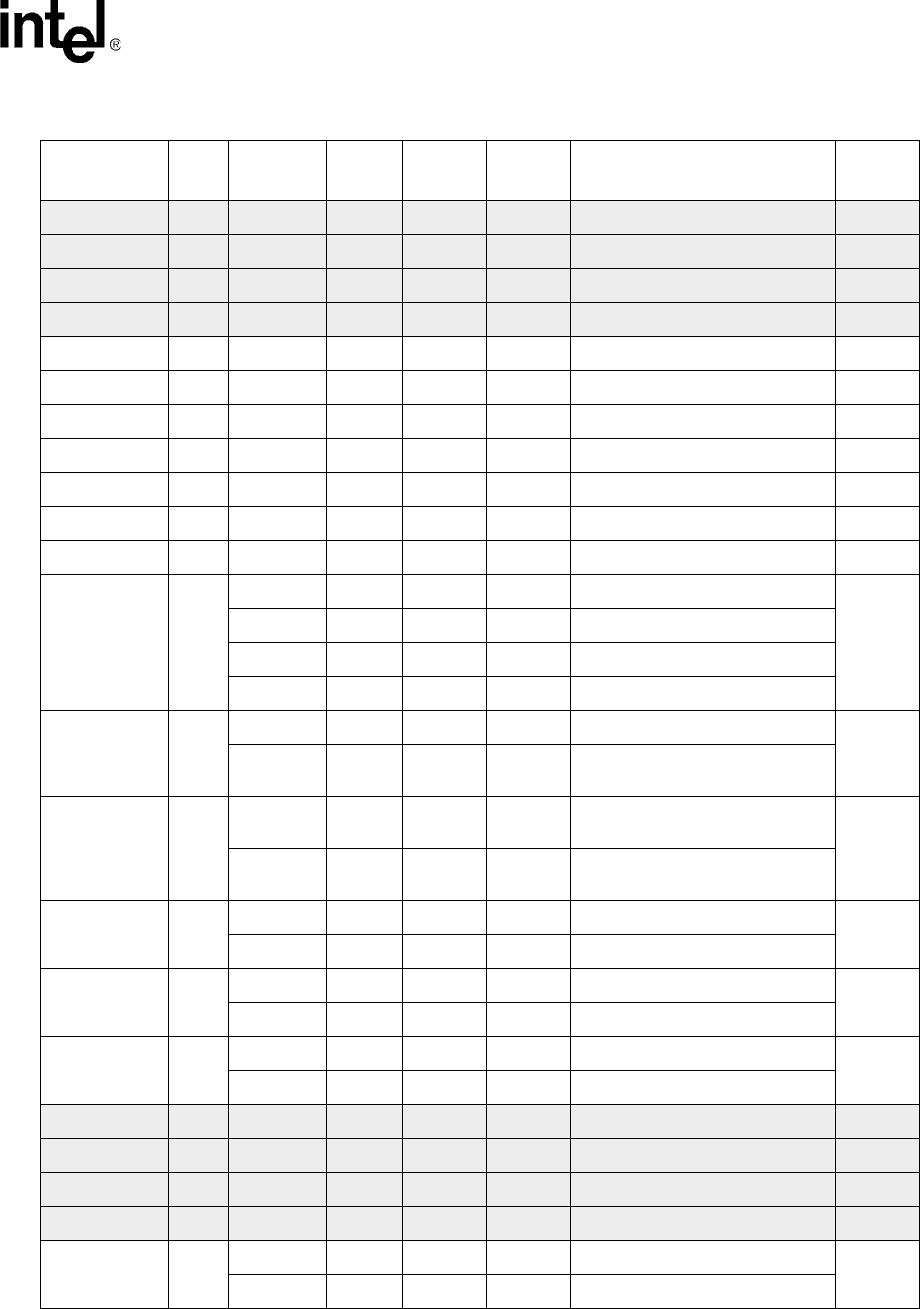

PXA250 and PXA210 Applications Processors Design Guide 8-9

Power and Clocking

GP11 1 3.6 MHz 3.6 MHz oscillator out VCCQ

GP12 1 32 KHz 32 KHz out VCCQ

GP13 1 MBGNT memory controller grant VCCQ

GP14 1 MBREQ Alternate Bus Master Request VCCQ

GP16 1 PWM0 PWM0 output VCCQ

GP17 1 PWM1 PWM1 output VCCQ

GP23 1 SCLK SSP clock VCCQ

GP24 1 SFRM SSP Frame VCCQ

GP25 1 TXD SSP transmit VCCQ

GP26 1 RXD SSP receive VCCQ

GP27 1 EXTCLK SSP ext_clk VCCQ

GP28 1

BITCLK AC97 bit_clk

VCCQ

BITCLK I2S bit_clk

BITCLK I2S bit_clk

BITCLK AC97 bit_clk

GP29 1

SDATA_IN0 AC97 Sdata_in0

VCCQ

SDATA_

IN

I2S Sdata_in

GP30 1

SDATA_

OUT

I2S Sdata_out

VCCQ

SDATA_

OUT

AC97 Sdata_out

GP31 1

SYNC I2S sync

VCCQ

SYNC AC97 sync

GP32 1

SYSCLK I2S sysclk

VCCQ

SDATA_IN1 AC97 Sdata_in1

GP34 1

FFRXD FFUART receive

VCCQ

MMCCS0 MMC Chip Select 0

GP35 1 CTS FFUART Clear to send VCCQ

GP36 1 DCD FFUART Data carrier detect VCCQ

GP37 1 DSR FFUART data set ready VCCQ

GP38 1 RI FFUART Ring Indicator VCCQ

GP39 1

MMCCS1 MMC Chip Select 1

VCCQ

FFTXD FFUART transmit data

Table 8-6. PXA250 and PXA210 VCCN vs. VCCQ (Sheet 4 of 6)

Pin

Pin

Count

Alt_fn

1-(in)

Alt_fn

2-(in)

Alt_fn

1-(out)

Alt_fn

2-(out)

Signal Description and

Comments

Power

Supply