8-6 PXA250 and PXA210 Applications Processors Design Guide

Power and Clocking

• Drive the PEXTAL pin with a digital signal that has a low level near 0 V and a high level near

VCC. Do not exceed VCC or go below VSS by more than 100 mV. The minimum slew rate is

1 V per 100 ns. The maximum current drawn by the external clock source when the clock is at

its maximum positive voltage should be about 1 mA.

• Float the PXTAL pin or drive it complementary to the PEXTAL pin, using the same voltage

level, slew rate, and input current restrictions. If floated, some degree of noise susceptibility

will be introduced in the system, and it is therefore not recommended.

8.5 Reset and Power AC Timing Specifications

The applications processor asserts the nRESET_OUT pin in one of several modes:

• Power On

• Hardware Reset

• Watchdog Reset

• GPIO Reset

• Sleep Mode

The following sections give the timing and other specifications for the entry and exit of these

modes.

8.5.1 Power Supply Connectivity

The PXA250 applications processor requires two or three externally-supplied voltage levels.

VCCQ requires high voltage, VCCN requires high or medium voltage, and VCC and PLL_VCC

require low voltage. PLL_VCC must be separated from other low voltage supplies. Depending on

the availability of independent regulator outputs and the desired memory voltage, VCCQ may have

to be separated from VCCN. VCCN does not have to be separated at the board level.

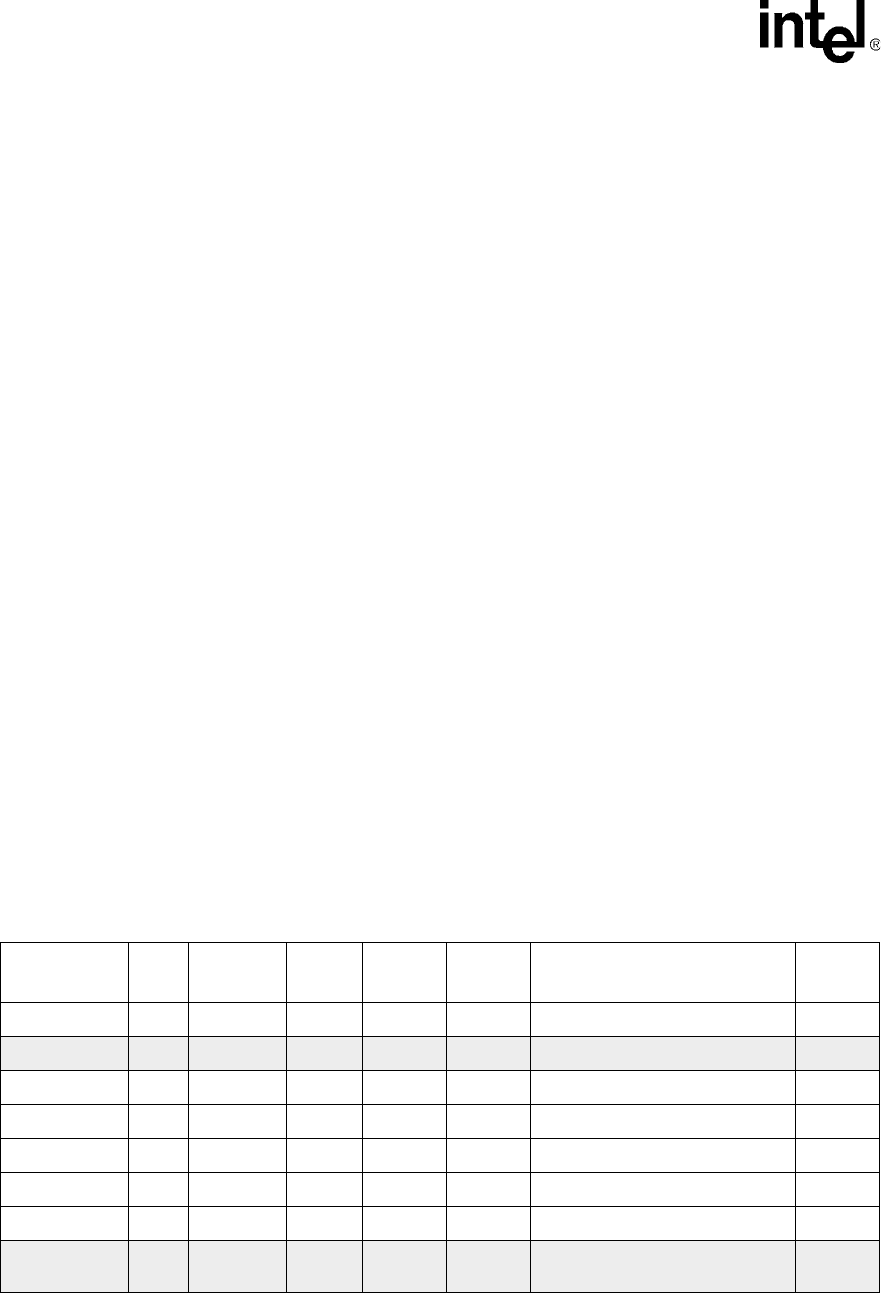

Note: Shaded sections are not supported for the PXA210 applications processor.

Table 8-6. PXA250 and PXA210 VCCN vs. VCCQ (Sheet 1 of 6)

Pin

Pin

Count

Alt_fn

1-(in)

Alt_fn

2-(in)

Alt_fn

1-(out)

Alt_fn

2-(out)

Signal Description and

Comments

Power

Supply

MA(25:0) 26 Main Memory Address Bus VCCN

MD(31:16) 16 Main Memory Data Bus (high) VCCN

MD(15:0) 16 Main Memory Data Bus (low) VCCN

nOE 1 Main Memory Bus Output Enable VCCN

nWE 1 Main Memory Bus Write Enable VCCN

nSDRAS 1 Main Memory Bus RAS VCCN

nSDCAS 1 Main Memory Bus CAS VCCN

DQM(3:2) 2

Main Memory Bus SDRAM byte

selects

VCCN