8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Pg. 11

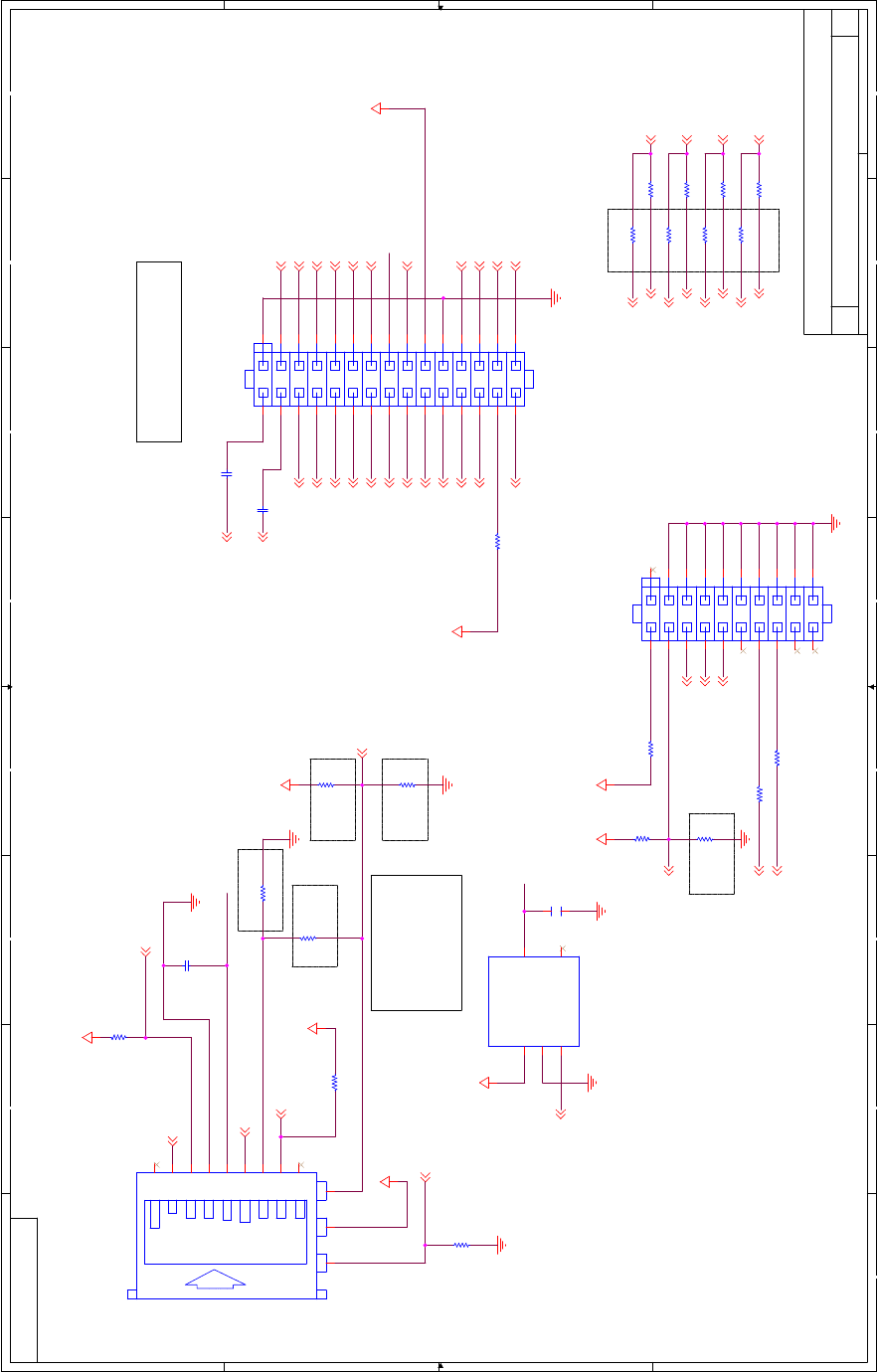

DNI IF MMC

DNI

IF

MMC

DNI

IF

SD

DNI

IF

SD

CARD Selection Resistors

and Values

RES SD MMC

R226 DNI 0

R227 DNI 100K

R225 0 DNI

R228 100K DNI

LAYOUT NOTE: Place close to

Battery Header and Codec UCB

1400

SD Socket

JTAG ICE Connector

Radio

Baseband

Connector

Copyright 2002 Intel Corporation

DNI

DNI

2.07

PXA250 Processor Reference Design

B

11 16Tuesday, February 05, 2002

Size Rev

Date: Sheet

of

MMC_PWR

MMC_PWR

RADIO_SPKRN

SA_MMCCLK {2}

MMC_ON{13}

SA_MMDAT{2}

MMC_CS0 {2}

nMMC_DETECT{2,13}

SA_MMCMD {2}

MMC_WP {2}

RADIO_DSR {2}

SA_BT_CTS {2}

SA_BT_RXD {2,15}

RADIO_RI {2}

RADIO_SPKRP {8}

RADIO_DTR{2}

SA_BT_RTS{2}

SA_BT_TXD{2,15}

RADIO_PWR_ON{6}

RADIO_WAKE{6}

MICGND{8,9}

RADIO_MICP{9}

VBATT{3,8,10,12,13,14}

VBATT{3,8,10,12,13,14}

RADIO_DCD{2}

JTAG_nTRST{3}

nRESET_IN{3,10,15}

JTAG_TMS{3,6,10,13}

JTAG_TCK{3,6,10,13}

SA_TDO{3,10}

CPLD1_TDI{6,10}

LINE_OUT_R{8}

LINE_OUT_L{8}

nRESET_OUT{3,6,13,15}

nRESET_IN {3,10,15}

RADIO_RXD_C{2}

GPIO_21{2,10}

DVAL_0 {15}

CPLD1_TDI{6,10}

DREQ_0 {15}

GPIO_19{2,10}

SA_TDO{3,10}

DREQ_1 {15}

GPIO_20{2,10}

JTAG_TCK{3,6,10,13}

DVAL_1 {15}

GPIO_22{2,10}

JTAG_TMS{3,6,10,13}

AC97_GPIO_0{8}

AC97_GPIO_3{8}

AC97_GPIO_1{8}

AC97_GPIO_4{8}

AC97_GPIO_2{8}

DC3P3V

DC5P5V

DC3P3V

DC3P3V

DC3P3V

DC3P3V

DC5P5V

DC3P3V

DC3P3V

R226

0

R218

0

10K

R270

R150

47.5K

Bottom Mount

CHECK !!

J10

1

2

3

4

5

6

7

8

10

11

9

12

CD_DAT3

CMD

VSS1

VDD

CLK

VSS2

DAT0

DAT1

WP

COMM

DAT2

CD

100K

R229

100K

R222

J20

9

87

65

43

20

2

19

1817

1615

1413

1211

10

1

21 22

23 24

25 26

27 28

29 30

J19

9

87

65

43

20

2

19

1817

1615

1413

1211

10

1

R233

0

R234

0

R235

0

MIC5207-3.3BM5

3.3V LDO REG

180ma

LE33

U27

3 4

5

2

1

EN BYP

VOUT

GND

VIN

R236

0

R223

75

C132

0.1UF

C140

0.1UF

R224

0

10KR147

R219

0

R231

0

R232

0

C91

0.1UF

100K

R227

100K

R228

R198

0

+

C92

4.7UF

12

R221

0

R225

0