PXA250 and PXA210 Applications Processors Design Guide 8-11

Power and Clocking

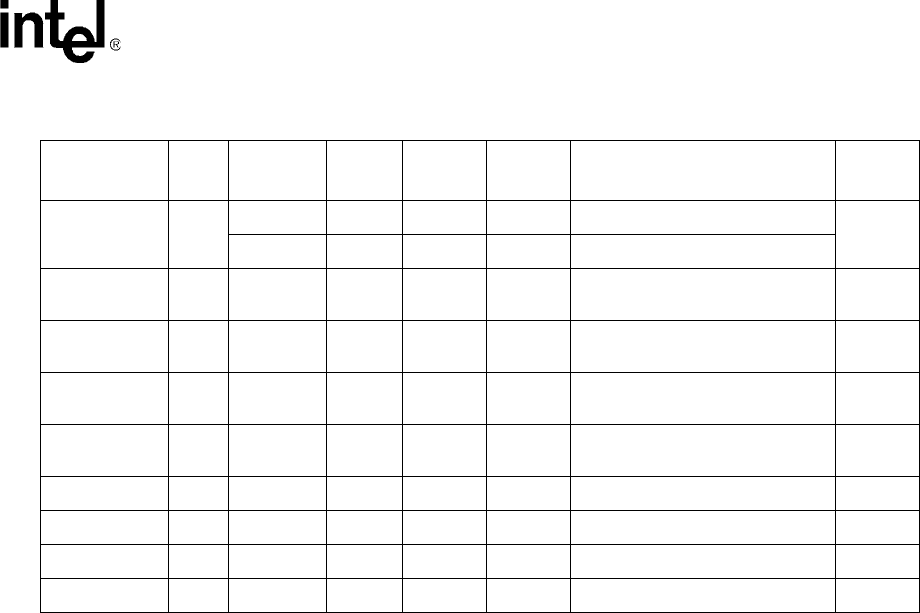

8.5.2 Power On Timing

The External Voltage Regulator and other power-on devices must provide the applications

processor with a specific sequence of power and resets to ensure proper operation. This sequence is

shown in Figure 8-1, “Power-On Reset Timing” on page 8-12 and detailed in Table 8-7, “Power-

On Timing Specifications” on page 8-12.

It is important that the applications processor power supplies be powered-up in a certain order to

avoid high current situations. The required order is:

1. VCCQ

2. VCCN

3. VCC and PLL_VCC

VCCN may be powered at the same time as VCCQ, however do not apply power to VCCN before

powering VCCQ.

GP73 1

LDD[15] LCD data pin 15

VCCQ

MBGNT memory controller grant

GP74 1

LCD_FCL

K

LCD Frame clock VCCQ

GP75 1

LCD_LCL

K

LCD line clock VCCQ

GP76 1

LCD_PCL

K

LCD Pixel clock VCCQ

GP77 1

LCD_AC

BIAS

LCD AC Bias VCCQ

PXTAL 1 3.6Mhz Crystal input 0.8 * VCC

PEXTAL 1 3.6Mhz Crystal output 0.8 * VCC

TXTAL 1 32khz Crystal input 0.8 * VCC

TEXTAL 1 32khz Crystal output 0.8 * VCC

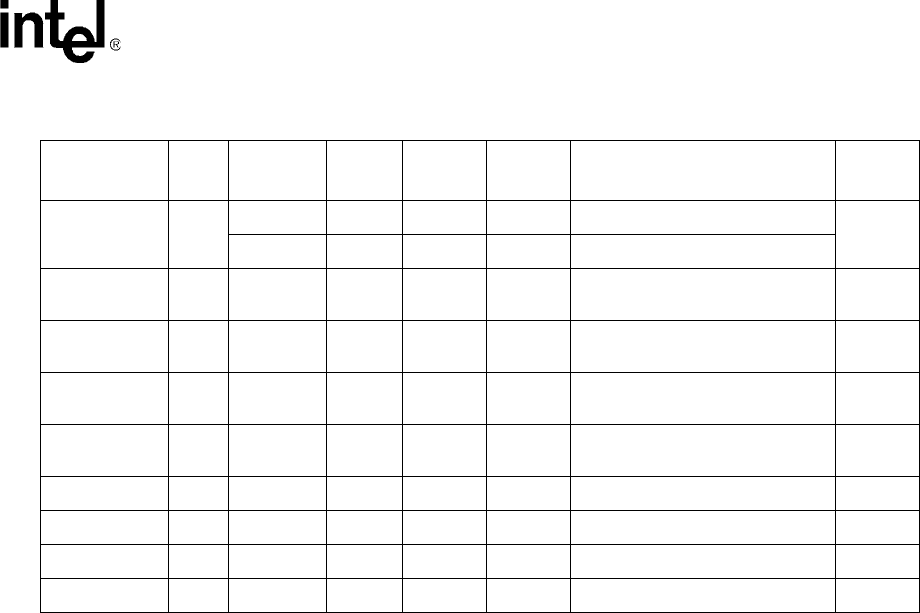

Table 8-6. PXA250 and PXA210 VCCN vs. VCCQ (Sheet 6 of 6)

Pin

Pin

Count

Alt_fn

1-(in)

Alt_fn

2-(in)

Alt_fn

1-(out)

Alt_fn

2-(out)

Signal Description and

Comments

Power

Supply