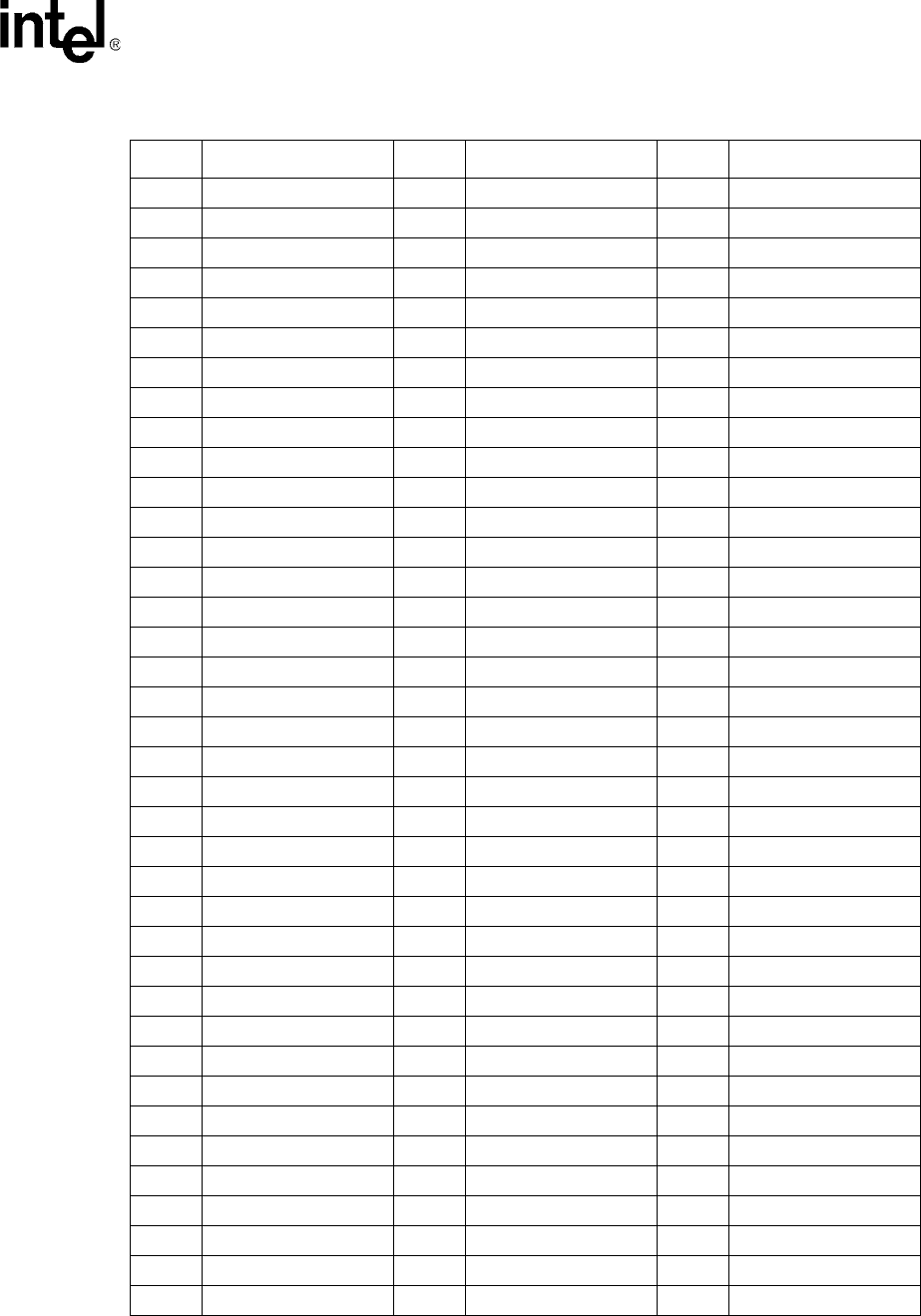

PXA250 and PXA210 Applications Processors Design Guide 1-17

Introduction

C8 VCCQ H8 VSS N8 VSSN

C9 SDATA_IN0/GPIO[29] H9 VSS N9 DQM[0]

C10 PWM[0]/GPIO[16] H10 VSSQ N10 VCCN

C11 USB_P H11 VCC N11 MD[12]

C12 BTTXD/GPIO[43] H12 VSSQ N12 VSSN

C13 VSSQ H13 VCC N13 nCS[5]/GPIO[33]

C14 VSS H14 PLL_VCC N14 GPIO[53]

C15 VCCQ H15 PLL_VSS N15 VCCN

D1 VCC J1 MA[5] P1 MA[17]

D2 VSSQ J2 MA[6] P2 VSSN

D3 SDCLK[1] J3 VSSN P3 VCCN

D4 L_DD[15]/GPIO[73] J4 MA[4] P4 MA[23]

D5 VCC J5 MA[3] P5 MD[0]

D6 L_DD[5]/GPIO[63] J6 VSSQ P6 VSSN

D7 L_DD[0]/GPIO[58] J7 VSS1 P7 MD[4]

D8 SPPSFRM/GPIO[24] J8 VSS1 P8 VCCN

D9 SDATA_OUT/GPIO[30] J9 VSS1 P9 nCS[2]/GPIO[78]

D10 SCL J10 VSSQ P10 MD[8]

D11 SDATA_IN1/GPIO[32] J11 nRESET P11 VCCn

D12 BOOT_SEL[1] J12 nRESET_OUT P12 MD[15]

D13 VSSQ J13 PWR_EN P13 VCCN

D14 VSSQ J14 nVDD_FAULT P14 GPIO[50]

D15 VSSQ J15 nBATT_FAULT P15 VSSQ

E1 nSDCAS K1 MA[8] R1 MA[19]

E2 VCCN K2 MA[9] R2 MA[20]

E3 VSSN K3 MA[10] R3 MA[21]

E4 SDCLK[0] K4 MA[7] R4 MA[25]

E5 L_DD[11]/GPIO[69] K5 VCCN R5 MD[1]

E6 L_DD[7]/GPIO[65] K6 VCC R6 VCCN

E7 L_DD[1]/GPIO[59] K7 VSSQ R7 MD[5]

E8 SSPTXD/GPIO[25] K8 VCC R8 nCS[0]

E9 SYNC/GPIO[31] K9 VSSQ R9 nCS[3]/GPIO[79]

E10 VCCQ K10 VCC R10 MD[9]

E11 MMCMD K11 GPIO[1] R11 VSSN

E12 VCCQ K12 TEXTAL R12 MD[14]

E13 VSSQ K13 TXTAL R13 nCS[4]/GPIO[80]

E14 VSSQ K14 PEXTAL R14 nPWE/GPIO[49]

E15 BOOT_SEL[2] K15 PXTAL R15 GPIO[51]

Table 1-5. PXA210 Applications Processor Pinout — Ballpad Number Order (Sheet 2 of 2)

Ball # Signal Ball # Signal Ball # Signal