PXA250 and PXA210 Applications Processors Design Guide 2-3

System Memory Interface

2.2 SDRAM Interface

The applications processor supports an SDRAM interface at a maximum frequency of 100 MHz.

The SDRAM Interface supports four 16-bit or 32-bit wide partitions of SDRAM. Each partition is

allocated 64 MBytes of the internal memory map. However, the actual size of each partition is

dependent on the particular SDRAM configuration used. The four partitions are divided into two

partition pairs: the 0/1 pair and the 2/3 pair. Both partitions within a pair (for example, partition 0

and partition 1) must be identical in size and configuration; however, the two pairs can be different.

For example, the 0/1 pair can be 100 MHz SDRAM on a 32-bit data bus, while the 2/3 pair can be

50 MHz SDRAM on a 16-bit data bus.

Note: For proper SDRAM operation above 50 MHz, 22 ohm series resistors must be placed on the

memory address lines.

2.3 SDRAM memory wiring diagram

Figure 2-2, “SDRAM Memory System Example” on page 2-4 is a wiring diagram example that

shows a system using 1Mword x 16-bit x 4-bank SDRAM devices for a total of 48 Mbytes. Refer

to Section 2.5, “SDRAM Address Mapping” on page 2-6 to determine the individual SDRAM

component address.

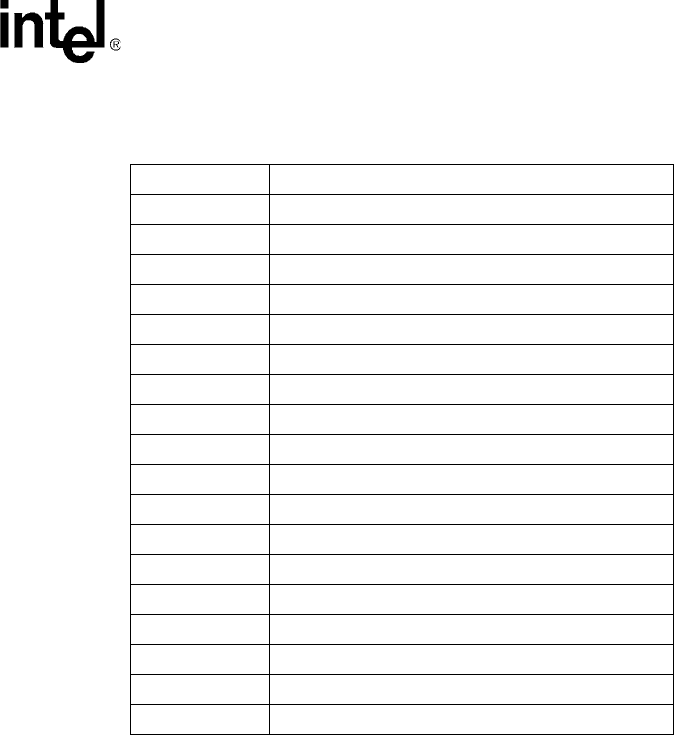

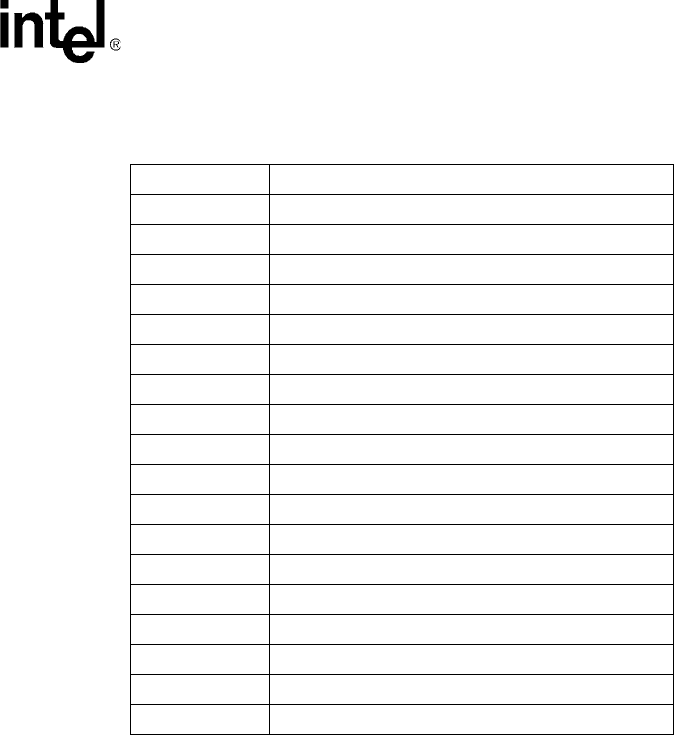

Table 2-1. Memory Address Map

0x6000 0000 Reserved Address Space

0x5C00 0000 Reserved Address Space

0x5800 0000 Reserved Address Space

0x5400 0000 Reserved Address Space

0x5000 0000 Reserved Address Space

0x4C00 0000 Reserved Address Space

0x4800 0000 Memory Mapped Registers (Memory Ctl)

0x4400 0000 Memory Mapped Registers (LCD)

0x4000 0000 Memory Mapped Registers (Peripherals)

0x3000 0000 PCMCIA/CF – Slot 1

0x2000 0000 PCMCIA/CF – Slot 0

0x1C00 0000 Reserved Address Space

0x1800 0000 Reserved Address Space

0x1400 0000 Static Chip Select 5

0x1000 0000 Static Chip Select 4

0x0C00 0000 Static Chip Select 3

0x0800 0000 Static Chip Select 2

0x0400 0000 Static Chip Select 1

0x0000 0000 Static Chip Select 0