SECTION 6 GPIB

6-21

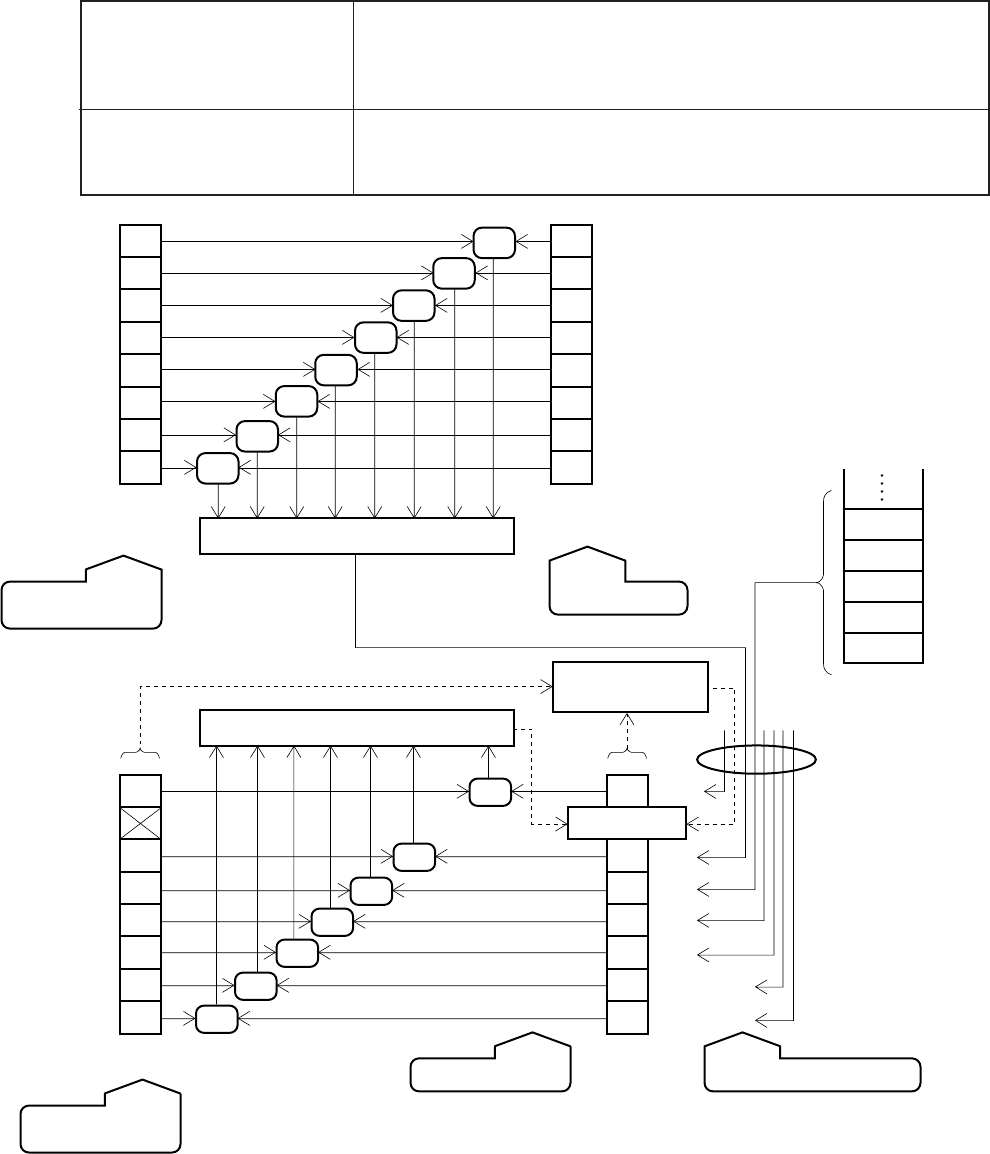

6.5.2 IEEE488.2-based status register

IEEE488.2 prescribes the following two status registers.

Status byte register Used to set the RQS and seven summary bits. Combined with a service

request enable register. SRQ bit is set on when ORs of both the status and

service request enable registers are not 0. RQS, reserved in bit 6, indicates

whether a service request is in an external controller.

Standard event status register Used to set eight types of standard events the device encounters. The

logical OR output bit is summarized in bit 5 of the status byte register as a

summary message of the event status bit (ESB).

Standard Status Model Diagram

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

&

&

&

&

&

&

&

&

7

5

4

3

2

1

0

7

6

5

4

3

2

1

0

&

&

&

&

&

&

&

Standard event

status enable

register

Logical OR

Power-on (PON)

User request (URQ)

Command error (CME)

Execution-time error (EXE)

Device dependent error (DDE)

Query error (QYE)

Bus control right request (RQC, not used)

End of operation (OPC)

Standard event

status register

Set by *ESE<n>

Read by *ESE?

Read by * ESR?

Data

Data

Data

Data

Data

Service request

occurrence

Logical OR

Output queue

Status

summary

message

OPER

ESB

MAV

QUES

QUE

NOT USED

NOT USED

MSS RQS

Service request

enable register

Set by *SRE<n>

Read by * SRE?

Read by *STB?

Status byte

register

Read by serial pole