HD151TS207SS

Rev.1.00, Apr.25.2003, page 24 of 38

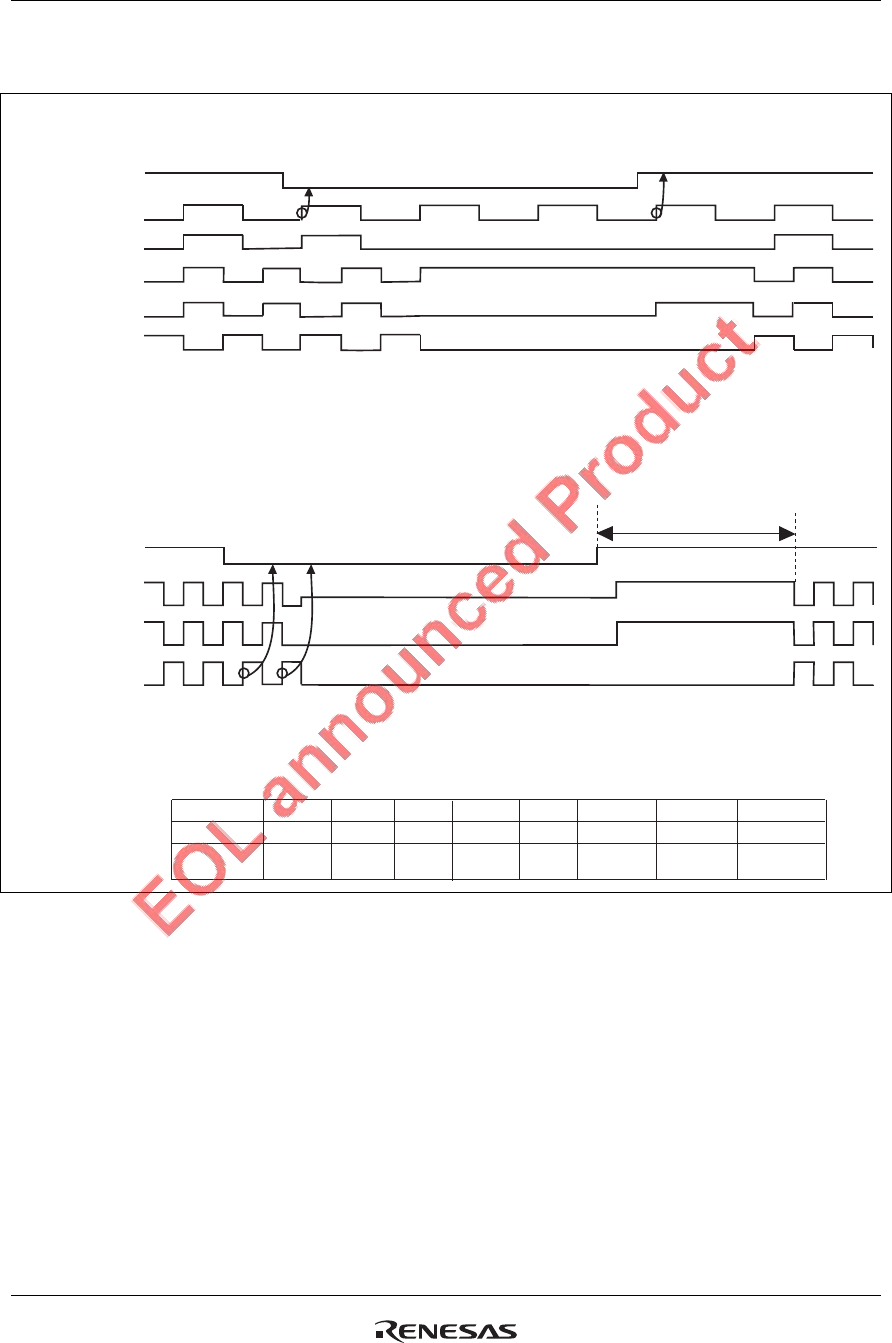

Clock Stop Timing Diagram

6

×

Iref (Controled b

y

B

y

te2[6]

)

2× Iref (Controled by Byte2[5:3])

Tristate (Controled by Byte2[6])

Tristate

PCI_STOP#

PCI_F

PCI

SRC (Stoppable)

PCI_STOP# Assertion/De-assersion

PCI_STOP# Assertion/De-assertion Waveforms

Low

PWRDWN#

CPU (Stoppable)

CPU# (Stoppable)

CPU (Stoppable)

PWRDWN# Assertion/De-assersion

PWRDWN# Assertion/De-assertion Waveforms

6× Iref

6× Iref

< 1.8 ms

PWRDWN#

PWRDWN# Functionality

CPU#CPU SRC SRC# 3V66

66MHz

Normal Normal Normal

Float Float Low

PCIF/PCI

33MHz

Low

USB/DOT

48MHz

Low

REF

14.318MHz

Low

SRC (Stoppable)

SRC# (Stoppable)

Float (Controled by Byte2[5:3])

Float

1 Normal

Iref:2

or Float

Iref:2

or Float

0