NI 5421 Specifications 18 ni.com

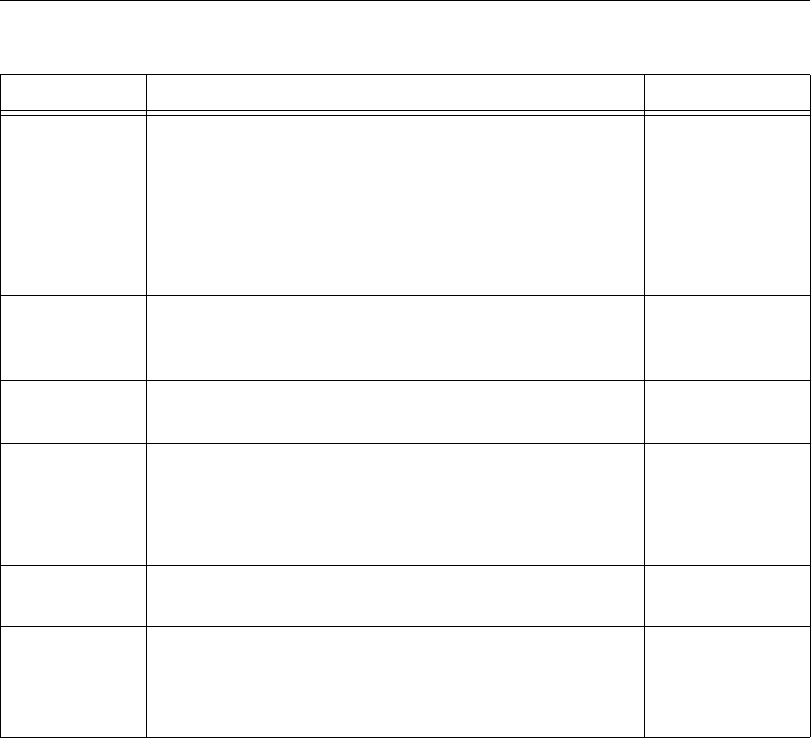

Phase-Locked Loop (PLL) Reference Clock

Table 4.

Specification Value Comments

Sources 1. NI PXI-5421—PXI_CLK10 (backplane connector)

NI PCI-5421—RTSI_7 (RTSI_CLK)

2. CLK IN (SMB front panel connector)

The PLL

Reference Clock

provides the

reference

frequency for the

phase-locked

loop.

Frequency

Accuracy

When using the PLL, the Frequency Accuracy of the

NI 5421 is solely dependent on the Frequency Accuracy

of the PLL Reference Clock Source.

—

Lock Time Typical: 70 ms.

Maximum: 200 ms.

—

Frequency

Range

5 MHz to 20 MHz in increments of 1 MHz.

Default of 10 MHz.

The PLL Reference Clock Frequency has to be accurate

to ±50 ppm.

—

Duty Cycle

Range

40% to 60% —

Exported PLL

Reference

Clock

Destinations

1. PFI<0..1> (SMB front panel connectors)

2. NI PXI-5421—PXI_Trig<0..7> (backplane connector)

NI PCI-5421—RTSI<0..7>

—